# CONVERSÃO DSB/SSB A CAPACITORES CHAVEADOS USANDO TRANSFORMADORES DE HILBERT RECURSIVOS

José Gabriel R. C. Gomes<sup>\*</sup> gabriel@ece.ucsb.edu

Antonio Petraglia<sup>†</sup> petra@pads.ufrj.br

\*Electrical and Computer Engineering Department, University of California at Santa Barbara Santa Barbara CA 93106-9560, USA.

<sup>†</sup>Programa de Engenharia Eletrica, PADS/COPPE, EPoli – Universidade Federal do Rio de Janeiro Caixa Postal 68504, CEP 21945-970, Rio de Janeiro, Brasil.

# **ABSTRACT**

This work presents the complete implementation of a switched-capacitor double-sideband (DSB) to singlesideband (SSB) converter, using discrete components. In order to obtain efficient SSB modulation, a Hilbert Transformer has been used. The implementation of the Hilbert Transformer through recursive allpass transfer functions allows good dynamic range and low sensitivity to errors on implemented capacitance ratios. The sampling rate of the SSB signal can be halved without loss of information, leading to circuit complexity reduction and savings in power consumption. Experimental results are provided, to verify the complete DSB to SSB conversion. A few practical aspects concerning the possible monolithic CMOS implementation of this circuit are considered.

**KEYWORDS**: Switched-capacitor filter, DSB to SSB conversion, Hilbert transformer, multirate.

# **RESUMO**

Neste trabalho é apresentada a implementação completa de um conversor de modulação DSB (doublesideband) para SSB (single-sideband) a capacitores cha-

Artigo submetido em 07/12/00 1a. Revisão em 17/04/01; 2a. Revisão em 15/04/02 Aceito sob recomendação do Ed. Assoc. Prof. José R. C. Piqueira veados, usando componentes discretos. Para se conseguir uma modulação SSB eficiente, um Transformador de Hilbert é utilizado. Uma boa faixa dinâmica e sensibilidade baixa ao erros nas razões de capacitâncias são conseguidas pela implementação do Transformador de Hilbert através de circuitos com funções de transferência recursivas do tipo passa-tudo. A taxa de amostragem do sinal SSB pode ser reduzida por um fator igual a 2 (dois) sem perda de informação, reduzindo a complexidade do circuito e o seu consumo de energia. A conversão de DSB para SSB completa é ilustrada pela apresentação de resultados experimentais. Alguns aspectos práticos relacionados à possível implementação monolítica CMOS deste circuito são considerados.

**PALAVRAS-CHAVE**: Filtros a capacitores chaveados, conversão DSB/SSB; transformador de Hilbert; processamento de sinais multitaxas.

### **INTRODUÇÃO** 1

No estágio de frequência intermediária (FI) de transmissores e receptores portáteis modernos, o grande número de canais simultâneos faz com que a segunda freqüência intermediária (FI<sub>2</sub>) seja muito menor do que FI. O canal-imagem em FI-FI<sub>2</sub> pode ter uma amplitude até 20 dB acima daquela do canal desejado, situado em FI+FI<sub>2</sub> (Crols e Steyaert, 1995), causando interferência inaceitável na demodulação, e deve ser portanto rejei-

tado. Quando um esquema heteródino coerente empregando somente uma senóide é usado para a demodulação de FI para FI<sub>2</sub>, um filtro passa-banda (FPB) extremamente seletivo precisa ser utilizado para o cancelamento do sinal indesejado em FI-FI<sub>2</sub>, e também sua parte negativa em -FI+FI<sub>2</sub>, de modo a reduzir a interferência na demodulação. A implementação integrada do FPB, que tipicamente possui um fator de qualidade elevado, exige grande área em circuito integrado. Por outro lado sua implementação externa aumenta o consumo de potência e os custos de produção.

As especificações do FPB foram simplificadas pelo desenvolvimento de conversores com rejeição de imagem (Abidi, 1995). Neste esquema, duas formas de onda senoidais com 90° de defasagem demodulam o sinal de entrada de FI em componentes I (em fase) e Q (em quadratura) as quais, antes de serem somadas, são filtradas através de uma rede de defasagem (RD) de 90°. para eliminar a imagem em ±FI2, enquanto que o sinal desejado reaparece com o dobro da sua amplitude de entrada. Por isso, o FPB pode ser projetado com especificações mais relaxadas, para uma implementação monolítica. Este esquema pode ser considerado como o dual do método de cancelamento seletivo de bandas laterais, aplicado em transmissores SSB (Abidi, 1995). Nestes sistemas, a complexidade de um FPB suficientemente seletivo para bloquear uma das bandas laterais do sinal, e deixar passar a outra, é evitada pelo uso de uma estrutura mais eficaz, na qual uma RD de  $90^{\circ}$  com banda larga participa de forma fundamental, ao gerar quadratura em todas as componentes em frequência dos sinais  $I \in Q$ . A eficiência destes sistemas depende fortemente da capacidade da RD em simultaneamente gerar defasagem de 90° e resposta em magnitude constante nas linhas  $I \in Q$ , sobre toda a faixa de frequências de interesse (Steyaert e Roovers, 1992).

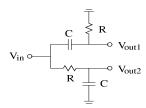

Uma técnica simples de produção de quadratura, comumente utilizada em receptores de rejeição de imagem, consiste em passar o sinal por um par integrador/diferenciador RC que introduz defasagens de  $+45^{\circ}$ , ilustrado na Fig. 1. Infelizmente, o balanceamento de magnitude entre as linhas I e Q depende fortemente da frequência, já que um dos ramos é a saída de um filtro passa-baixas, enquanto que o outro é saída de um filtro passa-altas. Na prática, imprecisões nos valores reais de R e de C causam descasamentos adicionais de fase e de magnitude entre as linhas, reduzindo ainda mais a taxa de rejeição de imagem (IRR). Uma avaliação de recentes implementações mostra que uma IRR superior a 35 dB é ainda difícil de ser atingida com esta técnica (Pun et al., 1998). O erro de quadratura pode ser corrigido em parte, porém ao custo de alguma forma de com-

Figura 1: Uma rede RC-CR de defasagem de 90°.

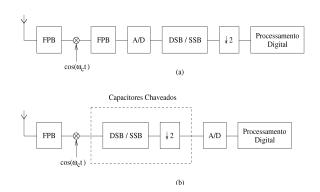

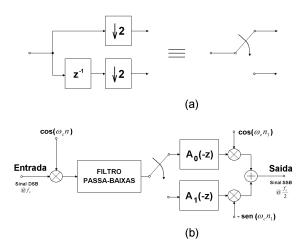

pensação, como por exemplo ajustes diretos (trimming) sobre o circuito integrado (Abidi, 1995 e Lee, 1998, Sec. 18.2.6). Para eliminar estas dificuldades, o modulador SSB apresentado por Hawley et al., 1995, propõe a separação I/Q no domínio digital. O diagrama de blocos básico desta implementação digital pode ser visto na Fig. 2(a). Entretanto, uma das desvantagens de tal solução, e de receptores de FI digitais em geral, é a exigente performance requerida do conversor A/D em termos de faixa dinâmica e consumo de potência (Razavi, Sec. 5.2.4). Detalhes adicionais sobre este assunto e comparações são apresentados na Sec. 4.

Este artigo concentra-se no uso eficiente de uma RD de 90° para modulação SSB no domínio analógico em tempo discreto. Na Sec. 2, é feita uma breve revisão do fato de que filtrar uma següência de valores reais (sinal amostrado) por uma RD de 90º de banda larga gera um sinal analítico, com valores complexos, cujo espectro, idealmente, é igual a zero para frequências negativas e igual ao espectro do sinal de entrada para freqüências positivas. O sinal analítico pode então ser processado e convertido ao domínio digital na metade da taxa de amostragem da entrada, sem quaisquer efeitos de aliasing, já que todas as componentes negativas foram eliminadas (Gomes e Petraglia, 2000). Consequentemente, podem ser obtidas especificações menos exigentes para os circuitos de FI, incluindo o conversor A/D, resultando

Figura 2: Receptores de FI com cancelamento seletivo de canal imagem: (a) Implementação digital (b) Implementação a capacitores chaveados.

principalmente em menor consumo de potência e maiores níveis de integração. Ainda na Sec. 2, é relembrado que um Transformador de Hilbert pode ser usado para a implementação de uma RD de 90° de banda larga, com casamento preciso de ganho e fase entre as linhas  $I \in Q$ , tendo um grande número de aplicações práticas (Hawley et al., 1995; Gold et al., 1970; Web e Kelly, 1978 e Tsui. 2001).

Um estudo comparativo (Schüssler e Weith, 1987) mostrou que Transformadores de Hilbert discretos recursivos (IIR) têm vantagens, no que diz respeito ao número de operações aritméticas e atraso total, quando comparados aos Transformadores baseados em estruturas FIR (Hawley, 1995; Web e Kelly, 1978). Para aplicações na faixa de FI, o Transformador de Hilbert IIR pode ser projetado usando técnicas de capacitores chaveados (SC) simples, porém precisas, para uma implementação monolítica de baixo consumo e pequena área (Petraglia et al., 1998). O projeto usando filtros SC estruturalmente passa-tudo, conforme mostrado na Sec. 3, leva à boa faixa dinâmica da RD e reduzida sensibilidade de sua resposta em frequência tanto aos erros nas razões de capacitâncias dos processos de fabricação CMOS como também ao ganho DC finito dos amplificadores operacionais, garantindo melhor casamento I/Q do que as redes RC-CR convencionais. O Transformador de Hilbert é agui considerado como um caso particular de filtro de meia-banda (Sec. 2) (Jackson, 1975; Ansari, 1987 e Regalia, 1993), o que permite (i) que os sinais I e Q sejam sub-amostrados por 2 já na entrada da rede de defasagem e (ii) que Transformadores de Hilbert IIR com fase aproximadamente linear sejam projetados (Petraglia et al., 1998).

De forma a validar o método de projeto proposto, são apresentados na Sec. 3 uma descrição detalhada e resultados experimentais da implementação de um protótipo do conversor DSB/SSB completo, usando componentes discretos. Multiplicadores a capacitores chaveados foram projetados para os estágios de conversão, e um filtro a capacitores chaveados elíptico de  $5^{\underline{a}}$  ordem, também baseado em blocos IIR estruturalmente passa-tudo, foi usado no estágio de filtragem passa-baixa (Cañive et al., 2000). Uma IRR acima de 40 dB foi obtida experimentalmente, e pode ser ainda aumentada em implementações integradas pelo simples uso de técnicas bem conhecidas de layout, conforme mencionado na Sec. 4. Estes resultados indicam que os blocos básicos do conversor DSB/SSB proposto, em particular o Transformador de Hilbert IIR, são boas alternativas práticas para o processamento de sinais em FI em receptores e transmissores portáteis. Algumas considerações de projeto envolvendo uma possível realização monolítica CMOS deste sistema

são apresentadas na Sec. 4. As conclusões seguem na Sec. 5.

### 2 FILTROS DE MEIA-BANDA COMPLE-**XOS IIR**

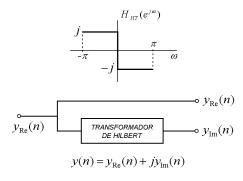

Um sinal analítico discreto no domínio do tempo y(n)é definido no domínio da freqüência como sendo igual a zero para  $-\pi < \omega < 0$  e diferente de zero para 0 < $\omega < \pi$ . Sinais reais têm seus espectros em freqüência simétricos em torno de  $\omega = 0$ , e portanto o sinal analítico y(n) sempre assume valores complexos (Mitra, 2000):

$$y(n) = y_{Re}(n) + jy_{Im}(n) \tag{1}$$

A parte imaginária de y(n) pode ser gerada filtrandose  $y_{Re}(n)$  através da função de transferência complexa (Mitra, 2000)

$$H_{HT}(e^{j\omega}) = \begin{cases} -j, & 0 \le \omega < \pi \\ j, & -\pi \le \omega < 0 \end{cases}$$

(2)

O filtro linear, discreto no domínio do tempo, que tem a sua resposta em frequência definida pela Eq. (2) é denominado Transformador de Hilbert ideal, como mostrado na Fig. 3. A partir das Eqs. (1) e (2), conclui-se que y(n) e  $y_{Re}(n)$  são relacionados no domínio da freqüência pelo filtro complexo

$$H(e^{j\omega}) = \begin{cases} 2, & 0 \le \omega < \pi \\ 0, & -\pi \le \omega < 0 \end{cases}$$

(3)

A função de transferência complexa definida pela Eq. (3) pode ser deslocada de  $\pi/2$  em direção à esquerda e também multiplicada por 1/2, de forma a originar a função de transferência real normalizada

Figura 3: Geração de um sinal analítico y(n) através de um Transformador de Hilbert.

$$G(e^{j\omega}) = \frac{1}{2}H(e^{j(\omega + \frac{\pi}{2})}) = \begin{cases} 1, & 0 < |\omega| < \pi/2 \\ 0, & \pi/2 < |\omega| < \pi \end{cases}$$

(4)

A função de transferência definida pela Eq. (4) representa um filtro passa-baixas de meia-banda ideal com coeficientes reais. Por causa da relação entre  $H(e^{j\omega})$ e  $G(e^{j\omega})$ , o filtro definido pela Eq. (3) é chamado de filtro de meia-banda complexo. Portanto, um filtro de meia-banda complexo pode ser projetado de uma forma simples, bastando deslocar a resposta em frequência de um filtro passa-baixas de meia-banda real de  $\pi/2$  para a direita e depois multiplicá-la por 2. Então, pela continuidade analítica das funções complexas des-critas pela Eq. (4), tem-se (Mitra, 2000)

$$H(z) = 2G(-jz) \tag{5}$$

## 2.1 Projeto de Filtros de Meia-Banda Complexos

Qualquer filtro passa-baixas, elíptico e de ordem ímpar G(z), cuja resposta em freqüência satisfaça às seguintes especificações:

i)

$$1 - \delta_p \le |G(e^{j\omega})| \le 1$$

, for  $0 \le \omega \le \omega_p$

ii)  $|G(e^{j\omega})| \le \delta_s$ , for  $\omega_s \le \omega \le \pi$  (6)

onde  $\omega_p + \omega_s = \pi$  e  $\delta_s^2 = 4\delta_p(1 - \delta_p)$ , pode ser expresso pela sua decomposição em duas componentes polifásicas (Vaidyanathan et al., 1987):

$$G(z) = \frac{1}{2} [A_0(z^2) + z^{-1} A_1(z^2)]$$

(7)

onde  $A_0(z)$  e  $A_1(z)$  são funções de transferência passatudo estáveis. É importante ressaltar que a igualdade da equação envolvendo  $\delta_p$  e  $\delta_s$  só seria exata se fosse possível utilizar, no projeto do filtro elíptico, a ordem exata estimada a partir das especificações, que é fracionária em geral. Ao arredondarmos a ordem para o menor número inteiro maior que o seu valor original, a igualdade em questão deixa de ser válida, fazendo com que os pólos se desloquem do eixo imaginário. Entretanto, um procedimento simples para reposicionar os pólos sobre o eixo imaginário, consiste de algumas iterações nas quais pequenos ajustes de  $\delta_p$  e  $\delta_s$  são realizados. Maiores detalhes sobre este procedimento são apresentados por

Vaidyanathan et al. (1987). Uma expressão matemática exata para as especificações de  $\delta_s$  e  $\delta_p$  recentemente desenvolvida, e a implementação de seu algoritmo em códigos para Matlab pode ser encontrada em Schüssler (2001). A Eq. (7), aplicada à Eq. (5), leva à seguinte expressão para H(z):

$$H(z) = A_0(-z^2) + jz^{-1}A_1(-z^2)$$

(8)

O projeto do filtro complexo de meia-banda IIR H(z)pode ser então dividido em três etapas:

- 1. Escolha de G(z) de acordo com as seguintes condições: filtro elíptico de meia-banda e ordem ímpar, projetado para satisfazer as especificações na Eq. (6). Esta etapa do projeto pode ser feita através de um algoritmo convencional para o projeto de filtros IIR, e algumas iterações como as mencionadas acima;

- 2. Decomposição polifásica de G(z) conforme a Eq. Para esta decomposição, foi utilizado um procedimento que permite a síntese de funções de transferência IIR através de funções de transferência passa-tudo associadas em paralelo (Mitra, 2000, Sec. 6.10). Ele é apresentado brevemente a seguir, por conveniência:

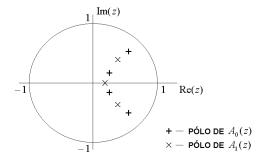

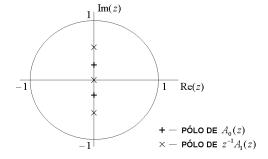

Quando a função de Transferência IIR passa-baixas (ou passa-altas) G(z) a ser implementada corresponde a um projeto Butterworth, Chebyshev ou Elíptico e é de ordem ímpar (que é o caso neste trabalho), existe um método simples para identificar os pólos de  $A_0(z)$  e  $A_1(z)$  a partir dos pólos  $\lambda_k \ (0 \le k \le N-1) \ \text{de } G(z)$ . Se  $\theta_k$  é o ângulo do pólo  $\lambda_k$ , os pólos de G(z) podem ser ordenados em ordem crescente de  $\theta_k$ , ou seja, de forma que  $\theta_k < \theta_{k+1}$ . Os pólos de  $A_0(z)$  são  $\lambda_{2k}$  e os pólos de  $A_1(z)$  são  $\lambda_{2k+1}$ . A Fig. 4 ilustra esta propriedade de entrelaçamento dos pólos de  $A_0(z)$  e  $A_1(z)$ .

Figura 4: Propriedade de entrelaçamento dos pólos de  $A_0(z)$  e  $A_1(z)$ , para um filtro passa-baixas de  $7^{\underline{a}}$  ordem.

Um caso mais particular acontece quando G(z) é elíptico, passa-baixas, tem ordem ímpar e é projetado aproximadamente a partir das condições propostas na Eq. (6) (Vaidyanathan et al., 1987). Nesta situação, todos os pólos de G(z) estão posicionados sobre o eixo imaginário do plano z (um dos pólos está na origem por causa da ordem ímpar do filtro).

Como consegüência, a decomposição polifásica de G(z) em  $A_0(z)$  e  $A_1(z)$  conforme a Eq. (7) é extremamente simples, porque o pólo na origem corresponde ao atraso unitário  $z^{-1}$  que multiplica  $A_1(z^2)$ e os demais pólos são imaginários, correspondendo aos termos  $z^2$  remanescentes em  $A_0(z^2)$  e  $A_1(z^2)$ . Esta decomposição é mostrada na Fig. 5.

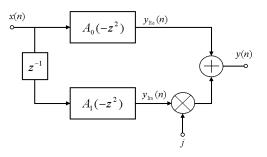

3. Finalmente, o filtro de meia-banda complexo H(z)é implementado conforme a estrutura mostrada na Fig. 6, usando as componentes polifásicas calculadas  $A_0(z^2)$  e  $A_1(z^2)$ . Deve-se ressaltar que as duas sequências de valores reais  $(y_{Re}(n) e y_{Im}(n))$ são geradas a partir do sinal de entrada real x(n). O sinal de saída complexo é obtido por y(n) = $y_{Re}(n) + jy_{Im}(n)$ . A função de transferência de x(n) para y(n) é o filtro de meia-banda complexo H(z) dado pela Eq. (3).

Portanto, H(z) pode ser implementado através da substituição de  $z^2$  por  $-z^2$  nas componentes polifásicas de G(z), como mostrado na Fig. 6. É importante observar que o diagrama de blocos na Fig. 6 é também uma realização de  $H_{HT}(z)$ , entre as saídas  $y_{Re}(n)$  e  $y_{Im}(n)$ , e isto pode ser usado para a modulação SSB, conforme será mostrado a seguir.

Figura 5: Decomposição polifásica de G(z) no caso particular da Eq. (6).

Figura 6: Diagrama de blocos de um filtro de meiabanda complexo IIR.

### 2.2 Modulação SSB com Transformador de Hilbert

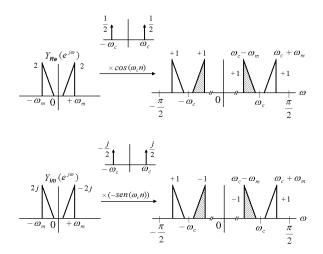

Para se obter a modulação SSB de um sinal real x(n), este é primeiro filtrado por H(z) conforme a Fig. 6. Como y(n) é analítico, o espectro em frequência  $Y_{Im}(e^{j\omega})$ é igual a $jY_{Re}(e^{j\omega})$  para  $-\pi \leq \omega < 0,$ e  $-jY_{Re}(e^{j\omega})$  para  $0 \le \omega < \pi$ . Multiplicando-se  $y_{Re}(n)$ por  $cos(\omega_c n)$ , o seu espectro é deslocado para  $-\omega_c$  e  $\omega_c$ e multiplicado por 1/2, como pode ser visto na parte esquerda da Fig. 7. Da mesma forma, multiplicando-se  $y_{Im}(n)$  por  $-sen(\omega_c n)$ , o espectro de  $y_{Re}$  é novamente deslocado para  $\pm \omega_c$ . Desta vez, a banda superior do seu espectro é multiplicada por 1/2, enquanto a banda inferior é multiplicada por -1/2 (parte direita da Fig. 7). Somando-se estes sinais modulados, as componentes de frequência correspondentes às bandas inferiores são canceladas e um sinal SSB de valores reais é obtido. O diagrama de blocos de um sistema de conversão DSB/SSB completo é mostrado na Fig. 8.

### 2.3 Decimação de $x_{SSB}(n)$

A redução da taxa de amostragem por um fator igual a dois (decimação por 2) é de particular interesse no caso do sinal modulado em SSB  $x_{SSB}(n)$ , porque a eliminação da banda inferior do sinal demodulado  $x_f(n)$  faz com que a banda passante de  $x_{SSB}(n)$  seja menor do que a metade da banda-passante de  $x_{DSB}(n)$ . Se  $x_{SSB}(n)$ também satisfaz a condição anti-aliasing  $\omega_c + \omega_m < \pi/2$ , a decimação por 2 torna possível amostrar  $x_{SSB}(n)$  com a metade da taxa de amostragem de  $x_{DSB}(n)$ , utilizando uma banda passante que é, no máximo, igual à banda passante de  $x_{DSB}(n)$  em termos do espectro em frequências de um sinal amostrado (de 0 a  $2\pi$ ). Ainda assim, é possível que a banda passante do sinal resultante  $x_{SSB}(2n)$  seja muito menor do que a banda passante de  $x_{DSB}(n)$ , caso o sinal  $x_f(n)$  seja passa-faixas.

Figura 7: Modulação SSB usando um Transformador de Hilbert.

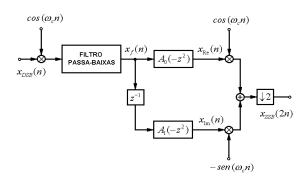

Já que a modulação por  $cos(\omega_c n)$  e  $-sin(\omega_c n)$  não emprega atraso algum nem operações de soma, o bloco decimador mostrado na Fig. 8 pode ser deslocado para a esquerda e colocado imediatamente antes dos filtros passatudo. De acordo com a identidade de Nobre (Strang e Nguyen, 1996), os filtros passa-tudo  $A_0(-z^2)$  e  $A_1(-z^2)$ são então substituídos por  $A_0(-z)$  e  $A_1(-z)$ . Além disso, a estrutura contendo dois decimadores e um atraso unitário na Fig. 9(a) pode ser substituída por uma simples chave multiplexadora, como ilustrado na Fig. 9(b). Os sinais de saída  $x_{SSB}(2n)$  das estruturas mostradas na Fig. 8 e na Fig. 9(b) são idênticos. Portanto, o diagrama de blocos da Fig. 9(b) torna-se uma solução muito eficiente para o problema da conversão DSB/SSB.

### IMPLEMENTAÇÃO EXPERIMENTAL 3

Com o objetivo de validar o método proposto, um conversor DSB/SSB completo usando um Transformador de Hilbert e técnica de capacitores chaveados foi proje-

Figura 8: Conversor DSB/SSB completo.

Figura 9: Simplificação do conversor DSB/SSB.

tado, simulado em um programa para a análise de circuitos chaveados, implementado com componentes discretos e testado em laboratório. O circuito do conversor DSB/SSB completo, mostrado na Fig. 9(b), é formado por quatro blocos básicos, que são um multiplicador de entrada, um filtro passa-baixas, um Transformador de Hilbert e um multiplicador/somador de saída, separadamente apresentados a seguir. Resultados experimentais são mostrados na Seção 3.5.

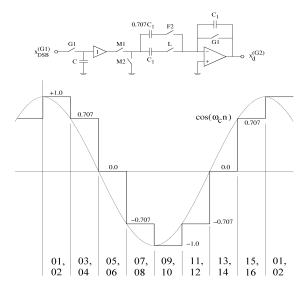

#### 3.1 Multiplicador de Entrada

O circuito na Fig. 10 é usado para gerar um sinal demodulado, em banda base, a partir do sinal de entrada DSB (e gera também imagens em  $\pm 2f_c$ , onde  $f_c$  é a freqüência da portadora). Este multiplicador usa uma forma de onda com 8 amostras, que representa um cosseno com frequência  $f_c = 500 \text{ Hz}$ . Portanto, a frequência de amostragem do multiplicador de entrada é igual a 4 kHz. O esquema das fases de *clock* das chaves é determinado por 16 intervalos adjacentes de tempo. Assim, os números de 1 a 16 que aparecem junto às chaves da Fig. 10 indicam os intervalos de tempo durante os quais a chave está fechada. Os capacitores que não têm indicação de valor têm capacitância normalizada igual a 1 (um).

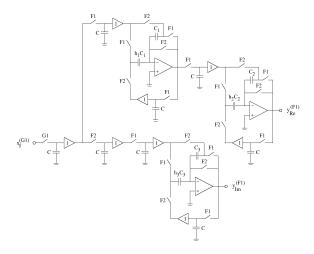

#### Filtro Passa-Baixas de 5<sup>a</sup> Ordem 3.2

Este filtro passa-baixas (ilustrado na Fig. 11) é usado para separar o sinal em banda base do sinal gerado na saída do multiplicador de entrada, e ele funciona a partir de duas fases de *clock* sem superposição,  $G_1$  e  $G_2$ , na mesma frequência de amostragem do multiplicador de entrada,  $f_s = 4$  kHz. O projeto da estrutura deste filtro elíptico, de  $5^{\underline{a}}$  ordem, foi mostrado por Petraglia e Monteiro (1998). Assim como o Transformador de Hil-

Figura 10: Multiplicador por cosseno.

bert, o seu projeto é baseado em seções estruturalmente passa-tudo (Petraglia e Monteiro, 1998). Isto significa que estas permanecem passa-tudo apesar dos erros de realização dos capacitores. Como consequência, baixa sensibilidade em relação às variações nas capacitâncias do circuito e elevada faixa dinâmica são obtidas. As funções de transferêcia das seções SC passa-tudo de primeira e segunda ordem são, respectivamente (Cañive et al., 2000):

$$A_{prim} = z^{-3/2} \frac{z^{-1} - (1-a)}{1 - (1-a)z^{-1}}$$

(9)

$$A_{seg} = z^{-1/2} \frac{z^{-2} - (2 - \alpha_1)z^{-1} + 1 - \alpha_2}{1 - (2 - \alpha_1)z^{-1} + (1 - \alpha_2)z^{-2}}$$

(10)

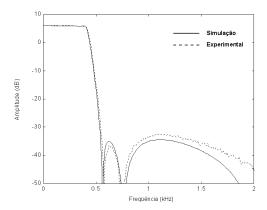

sendo que a realização física dos coeficientes  $a, \alpha_{1s}, \alpha_{2s}, \alpha_{1i}$  e  $\alpha_{2i}$  pode ser vista na Fig. 11. Esse filtro foi projetado para atender às seguintes especificações: faixa de passagem de 0 a 400 Hz  $(0.2\pi)$  com 0.1 dB de ripple, e faixa de rejeição iniciando em 600 Hz  $(0.3\pi)$  com atenuação mínima de 40 dB. Com estas especificações, os coeficientes calculados são:  $a=0.3578, \alpha_{1s}=0.5221, \alpha_{2s}=0.1165, \alpha_{1i}=0.6456$  e  $\alpha_{2i}=0.3960$ . A resposta em freqüência experimental deste filtro é mostrada na Fig. 15.

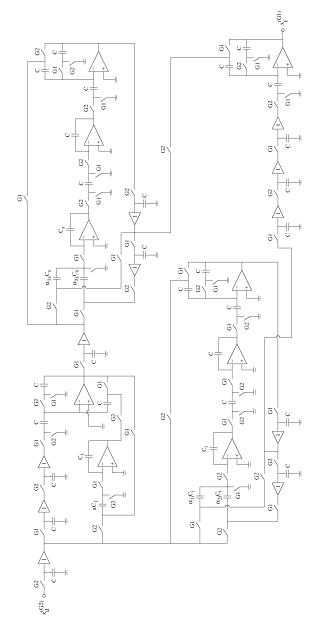

# 3.3 Transformador de Hilbert

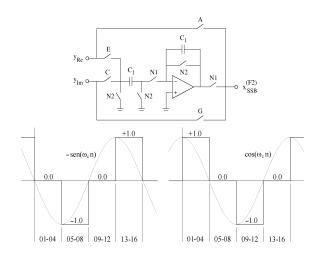

Este é o principal bloco do conversor DSB/SSB. O seu diagrama esquemático é mostrado na Fig. 12. O projeto dos filtros passa-tudo de primeira ordem, dois deles no caminho superior e um no caminho inferior, com o objetivo de realizar um Transformador de Hilbert entre as

saídas passa-tudo  $y_{Re}(n)$  e  $y_{Im}(n)$ , foi feito conforme a teoria apresentada na Seção 2.1. Este procedimento de projeto é explicado em maiores detalhes em Petraglia et al. (1998) e Mitra (2000). As funções de transferência passa-tudo são as seguintes:

$$A_0(z) = \frac{z^{-1} + 0.1907}{1 + 0.1907z^{-1}} \cdot \frac{z^{-1} + 0.8607}{1 + 0.8607z^{-1}}$$

(11)

$$A_1(z) = \frac{z^{-1} + 0.5531}{1 + 0.5531z^{-1}}$$

(12)

Figura 11: Filtro passa-baixas elíptico de  $5^{\underline{a}}$  ordem.

Figura 12: Transformador de Hilbert a capacitores chaveados usando seções passa-tudo de primeira ordem.

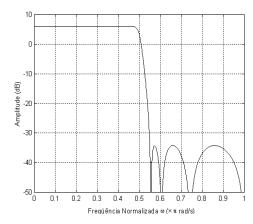

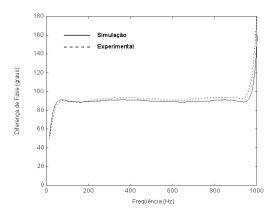

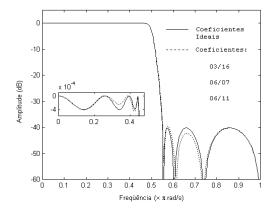

A Fig. 13 mostra a resposta em freqüência simulada do filtro de meia-banda real G(z), associado a  $A_0(z)$ e  $A_1(z)$  pelas Eqs. (7), (11) e (12). Através do uso de uma chave multiplexadora na entrada de ambos os filtros passa-tudo, a taxa de amostragem é então reduzida para  $f_s = 2 \text{ kHz}$ . Desta forma, a conversão de DSB para SSB é realizada na menor taxa de amostragem possível. As curvas teórica e experimental para a diferença de fase entre  $y_{Re}(n)$  e  $y_{Im}(n)$  são mostradas na Fig. 16, Seção 3.5.

Figura 13: Resposta em freqüência simulada do filtro de meia-banda real G(z).

### 3.4 Multiplicador/Somador de Saída

Este bloco, cujo circuito se encontra na Fig. 14, realiza duas multiplicações: a multiplicação do sinal de saída do passa-tudo superior,  $y_{Re}(n)$ , por um cosseno de 4 amostras  $(cos(\omega_c n))$  e a multiplicação do sinal de saída do passa-tudo inferior,  $y_{Im}(n)$ , por um seno de 4 amostras, com atraso de 180 graus  $(-sen(\omega_c n))$ . Os resultados destas multiplicações são somados, amostra por amostra. A frequência destes sinais senoidais é  $f_c = 500 \text{ Hz}$ . Quando eles são aplicados ao sinal em banda-base complexo gerado pelo Transformador de Hilbert, a soma das partes real e imaginária do sinal complexo geram um sinal modulado SSB com centro na frequência  $f_c = 500$ Hz, como na Fig. 7.

O multiplicador/somador tira proveito do fato de que estas formas de onda senoidais de 4 amostras podem ser representadas por valores simples: as amostras [0; -1; 0; 1] são usadas para representar o seno negativo, enquanto que as amostras [1;0;-1;0]são usadas para representar o cosseno. Portanto, o sinal de saída obtido pela multiplicação/adição  $x_{SSB}(n) =$  $-\sin(2\pi f_c n)y_{Re}(n) + \cos(2\pi f_c n)y_{Im}(n)$  é definido pela sequência  $\{+y_{Im}(n); -y_{Re}(n); -y_{Im}(n); +y_{Re}(n)\}.$

Figura 14: Multiplicador/somador.

### 3.5 **Resultados Experimentais**

Os circuitos integrados CD4016 (chaves analógicas CMOS) e TL072 (amplificadores operacionais) foram usados para a implementação do conversor DSB/SSB. Todos os dados experimentais foram adquiridos com um analisador de espectro HP3582A. A Fig. 15 mostra as respostas em frequência experimental e teórica obtidas para o filtro passa-baixas elíptico de  $5^{\underline{a}}$  ordem apresentado na Seção 3.2. A diferença de fase obtida entre os caminhos superior e inferior do Transformador de Hilbert, ou seja, entre  $y_{Re}(n)$  e  $y_{Im}(n)$ , é mostrada na Fig. 16, em uma curva obtida por simulação e outra experimental. Por causa da redução de taxa de amostragem mencionada na Seção 3.3, a frequência de amostragem é 2 kHz para o Transformador de Hilbert.

Figura 15: Resposta em freqüência do filtro passa-baixas elíptico de  $5^{\underline{a}}$  ordem.

O espectro em frequência do sinal de entrada aplicado ao conversor DSB/SSB nos testes experimentais é mostrado na Fig. 17(a) e o espectro em frequência do sinal de saída correspondente, na Fig. 17(b). Pode-se observar na Fig. 17(b) que a banda superior do sinal de entrada foi atenuada em 43,4 dB. Este resultado está em ótima concordância com o esperado devido à atenuação de 40 dB do filtro de meia-banda G(z) na Fig. 13. Pode-se notar também a presenca de um sinal espúrio na frequência central, gerada pela modulação de um offset de tensão DC pelo multiplicador/somador de saída. A amplitude deste sinal espúrio em 500 Hz, no caso da implementação usando componentes discretos, pode aumentar consideravelmente se não forem usados buffers para desacoplamento de tensão DC entre as saídas do Transformador de Hilbert e as entradas do multiplicador/somador de saída. Esse efeito pode ser consideravelmente reduzido no caso de uma implementação do conversor DSB/SSB em circuito integrado, através do uso de uma estrutura parcialmente ou integralmente diferencial (Willingham e Martin, 1990).

#### **CONSIDERAÇÕES SOBRE** IMPLE-MENTAÇÃO EM **CIRCUITO** INTE-**GRADO**

Nesta Seção serão feitas algumas considerações sobre a possível implementação monolítica do esquema mostrado na Sec. 3. O filtro passa-baixas de  $5^{\underline{a}}$  ordem foi implementado em circuito integrado para operação em frequências de vídeo, e os detalhes do projeto deste circuito podem ser vistos em Cañive et al. (2000). Este projeto tem como base a conexão de dois filtros passatudo em paralelo, de forma que baixa sensibilidade às variações no processo de fabricação e grande faixa dinâ-

Figura 16: Respostas em fase experimental e teórica do Transformador de Hilbert.

Figura 17: – Resultados experimentais: (a) Entrada e (b) Saída do Conversor DSB/SSB.

mica são conseguidas. Ele também inclui propriedades de testabilidade que permitem a detecção fácil de erros nos parâmetros implementados (Cañive e Petraglia, 2001). Esta propriedade é útil tanto no projeto como no teste do protótipo do conversor DSB/SSB.

Por causa da baixa sensibilidade do Transformador de Hilbert SC (Fig. 12) aos erros nas razões entre capacitâncias, os seus coeficientes ideais mostrados nas Eqs. (11) e (12) podem ser realizados usando arrays com um pequeno número de capacitores unitários. Como resultado, na implementação integrada do Transformador de Hilbert SC, razões inteiras de capacitâncias podem ser usadas para aproximar os valores ideais dos coeficientes. O termo inteiras significa que todos os capacitores são projetados de forma a serem múltiplos inteiros de um capacitor unitário. Apesar da baixa precisão do valor da capacitância unitária, razões inteiras de capacitâncias podem ser implementadas com alta precisão, em torno de 0.1% (Shyu et al., 1984 e McNutt et al., 1994). As razões de capacitâncias inteiras 3/16, 6/7 e 6/11 foram escolhidas para aproximar os coeficientes 0.1907, 0.8607 e 0.5531, respectivamente, o que requer um total de 49 capacitores unitários. O layout pode então ser feito sobre uma matriz quadrada com  $7 \times 7$  capacitores unitários, aumentando a precisão por minimizar efeitos de gradiente. As respostas em freqüência do filtro de meia-banda associado G(z), com coeficientes ideais e com coeficientes aproximados pelas razões de inteiros mencionadas, são comparadas na Fig. 18. Pode-se verificar que o desvio da resposta em frequência é desprezível tanto na faixa de passagem como na de rejeição, o que comprova a baixa sensibilidade do Transformador de Hilbert SC.

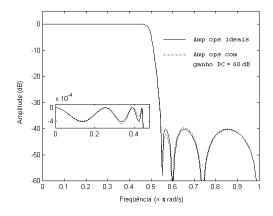

O circuito mostrado na Fig. 12 também apresenta baixa sensibilidade ao ganho DC finito dos amplificadores operacionais. A Fig. 19 mostra uma comparação entre as respostas em frequência de G(z) usando amplificadores operacionais ideais (com ganho DC infinito) e usando amplificadores operacionais com ganho DC igual a 60 dB. Estes resultados mostram que projetos de amplificadores operacionais mais simples e mais estáveis po-

dem ser usados, e também que se pode reduzir ganho DC para se aumentar a banda passante em aplicações de alta frequência (de 10 a 100 MHz, como por exemplo no caso do processamento de sinais em frequências intermediárias usando circuitos SC). Outros fatores nãoideais importantes, como por exemplo o ruído por injeção de carga e offsets de tensão, podem ser reduzidos por dimensionamento e layout cuidadosos. Investigações semelhantes foram feitas para o filtro passa-baixas elíptico de quinta ordem mostrado na Fig. 11, e podem ser encontradas em (Petraglia e Monteiro, 1998).

O fato de que a resposta em frequência do filtro de meiabanda apresenta desvios desprezíveis na presença de erros na implementação dos coeficientes e ganho DC finito dos amp ops é a principal razão para as diferenças de fase e de amplitude muito pequenas entre as linhas I e Q, isto é, o casamento entre ambas as linhas permanece preciso apesar de aspectos não-ideais da implementação. Portanto, as Figs. 18 e 19 proporcionam uma indicação alternativa do bom casamento I/Q, o que tem como resultado final a alta IRR observada.

O multiplicador de entrada com 8 amostras (Fig. 10) utiliza duas razões de capacitâcias: uma delas unitária, e a outra igual a 0.7071. Observou-se que esta última pode ser aproximada por 7/10 sem qualquer degradação perceptível na performance do conversor DSB/SSB. O coeficiente 1 do multiplicador/somador da Fig. 14 requer somente uma razão de capacitores iguais. É importante ter cuidado, entretanto, com o fato de que a modu-lação do offset de tensão deste amp op (na Fig. 14 faz com que uma componente espúria surja sobre a frequência da portadora, como foi visto na Fig. 17(b). Este fator não-ideal, bem como os efeitos de injeção de carga, podem ser reduzidos pelo uso de estruturas com-

Figura 18: Verificação da sensibilidade do filtro de meia banda complexo G(z) em relação aos seus coeficientes.

Figura 19: Efeito do ganho DC finito dos amplificadores operacionais na resposta em frequência do filtro G(z).

Figura 20: Diagrama de tempo para controle das chaves analógicas.

pletamente diferenciais, quasi-diferenciais ou com realimentação de erro (Willingham e Martin, 1990).

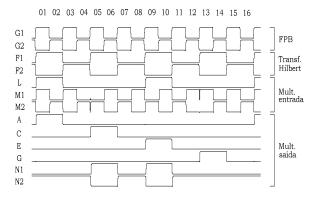

O controle das diversas chaves analógicas do circuito completo do conversor DSB/SSB é executado de acordo com o diagrama de tempo da Fig. 20. O conjunto completo de unidades lógicas utiliza um total de 202 transistores, podendo ser fabricado no mesmo circuito integrado do conversor DSB/SSB com custo adicional desprezível. Uma parte dos circuitos lógicos tem como função garantir a não-superposição de determinadas fases (por exemplo,  $F_1$  e  $F_2$ ) ou seja, que em nenhum momento estas fases estejam simultaneamente ativas. É também importante observar, comparando  $G_1$  e  $G_2$ com  $F_1$  e  $F_2$ , que esse diagrama explora o fato de que o Transformador de Hilbert da Fig. 12 opera na metade da taxa de amostragem do sinal de entrada. A Fig. 20 foi gerada por simulação elétrica de um circuito lógico projetado num processo CMOS 0.35 µm. Uma vez que a freqüência de chaveamento dos sinais mais rápidos desta simulação  $(G_1 ext{ e } G_2)$  é 40 MHz e todos os sinais digitais estão completamente estabilizados ao final de 25 ns, pode-se concluir que a frequência de chaveamento pode ainda ser facilmente estendida a valores próximos de 200 MHz ou superiores. Estes resultados aliados aos avanços tecnológicos obtidos nos processos de fabricação de circuitos integrados, que permitem que circuitos a capacitores chaveados operem em frequências de amostragem acima de 200 MHz (e.g., Baschiroto et. al, 2000), indicam que o processamento de sinais analógicos na faixa de FI (10 a 100 MHz) de transceptores modernos é realizável com a técnica aqui proposta.

# 4.1 Faixa Dinâmica, Consumo e Ruído

Como o Transformador de Hilbert da Fig. 12 é composto por filtros estruturalmente passa-tudo, os sinais

nas saídas dos amp ops terão amplitudes idênticas, independentemente dos erros nas razões de capacitâncias  $h_1, h_2$  e  $h_3$  que definem os coeficientes das Eqs. 11 e 12. Como consequência, uma boa faixa dinâmica pode ser conseguida. Pode-se comparar este resultado com outras aplicações práticas, nas quais o Transformador de Hilbert discreto é aproximado por longas linhas de atraso (Hawley et al., 1995 e Web e Kelly, 1978). Nestas aplicações, o espalhamento inevitavelmente alto dos coeficientes faz com que sinais com grande variedade de níveis de amplitude sejam somados para formar a saída, afetando particularmente o casamento I/Q e portanto reduzindo a IRR alcançável. Para lidar com este problema, uma representação interna de 18 bits foi usada no projeto do Transformador de Hilbert digital FIR em Hawley et al. (1995), de forma tal que o filtro de meiabanda correspondente seria teoricamente capaz de alcançar uma atenuação de 70 dB na faixa de rejeição. Fabricado em um processo CMOS 1  $\mu m$ , o protótipo tem uma área ocupada de 25.2 mm<sup>2</sup> e dissipa 1.8 W ao operar a 300 MHz com alimentação de 5 V. Os resultados experimentais anunciados, obtidos a uma taxa de amostragem mais baixa, indicam uma IRR em torno de 45 dB, resultado este que está próximo do obtido neste trabalho (Fig. 17(b)).

Considerando um processo CMOS  $0.8 \mu m$  com alimentação de 5 V, taxa de amostragem igual a 18 MHz, amplificadores operacionais de transcondutância em configuração cascode e coeficientes realizados em array de capacitores unitários (Cañive e Petraglia, 2001), o consumo do Transformador de Hilbert SC da Fig. 12 seria aproximadamente 51 mW e a área ocupada seria cerca de 1.2 mm<sup>2</sup>. Uma vez que o consumo dinâmico de um circuito digital aumenta linearmente com a frequência (Rabaey, 1996), o Transformador de Hilbert digital acima mencionado dissiparia em torno de 108 mW a 18 MHz. Uma economia substancial tanto na área de silício como no consumo de potência é portanto conseguida com o método proposto. Além disso, a complexi-dade do estágio de conversão A/D também é reduzida, já que ele pode ser posicionado após a conversão DSB/SSB e operado, por exemplo, a 18 MHz, as invés dos 36 MHz que seriam necessários caso um Transformador de Hilbert digital fosse usado.

Ruído do tipo *flicker* gerado por filtros e *mixers* é outro detalhe importante na implementação CMOS de circuitos de comunicação (Lee, 1998, Cap. 18), porque o espectro do sinal demodulado se estende a freqüências próximas de zero. No caso de filtros SC, o ruído térmico (de banda larga) gerado pela resistência de uma chave analógica fechada pode ter um espectro cuja largura de banda excede por diversas ordens de magnitude a freqüência de

reça amplificada em banda-base. O efeito de tais fontes de ruído pode ser reduzido por algumas técnicas usadas em conjunto. Especificamente, esquemas de codificação sem nível DC, que funcionam como filtros passa-altas sobre o sinal demodulado, removem parte da potência do ruído. Além disso, a potência do sinal pode ser aumentada nos estágios de RF, por exemplo pelo uso de mixers ativos ao invés de passivos (Razavi, 1998, Cap. 6). Por outro lado, já que os estágios que se seguem aos mixers operam em frequências mais baixas, dispositivos maiores podem ser usados para reduzir o ruído. Esta técnica pode ser prontamente aplicada aos circuitos SC apresentados neste artigo, conforme mencionado anteriormente nesta seção: por causa do pequeno espalhamento de capacitâncias e pequena sensibilidade da estrutura com relação às razões de capacitâncias, estas podem ser aproximadas por razões de pequenos números inteiros, o que permite aumentar o valor da capacitância unitária com o objetivo de reduzir o ruído, sem aumento significativo da área de silício. Um método semelhante foi aplicado por Barúqui et al. (2002). Finalmente, a dupla amostragem correlacionada, uma técnica familiar a projetistas de redes SC (Huang et al., 1997, e Nagari et al., 1997), é também eficiente na redução da potência de ruído em sistemas de comunicação.

amostragem, fazendo com que a potência do ruído apa-

#### 5 CONCLUSÕES

A teoria básica da modulação SSB usando filtros complexos de meia-banda IIR foi apresentada e, com base nesta teoria, um conversor completo de DSB para SSB a capacitores chaveados foi projetado, implementado com componentes discretos e testado em laboratório com taxa de amostragem  $f_s = 4$  kHz. Para simplificar a estrutura do conversor DSB/SSB, foi usada a decomposição polifásica de filtros de meia-banda em termos de seções passa-tudo. A utilização de filtros a capacitores chaveados estruturalmente passa-tudo permitiu uma elevada precisão na implementação do Transformador de Hilbert, praticamente eliminando a diferença entre as amplitudes dos canais I e Q, e minimizando o erro na defasagem de 90°. Multiplicadores a capacitores chaveados bastante simples foram projetados, com o objetivo de implementar a demodulação com  $cos(2\pi f_c n)$  e a modulação SSB com  $cos(2\pi f_c n)$  e  $-sin(2\pi f_c n)$ . Os resultados experimentais obtidos validaram o procedimento de projeto proposto, que pode ser aplicado à implementação de um conversor DSB/SSB completo em circuito integrado com tecnologia CMOS.

## AGRADECIMENTOS

Os autores agradecem o apoio financeiro fornecido pela CAPES e pelo CNPq ao desenvolvimento deste trabalho. Agradecem também ao Prof. F. A. P. Barúqui pelas discussões e sugestões, e ao Prof. A. C. M. de Queiroz pelo auxílio na utilização do seu programa ASIZ para a simulação de circuitos discretos no tempo.

# REFERÊNCIAS

- Abidi, A. (1995). Direct-conversion radio transceivers for digital communications, IEEE J. Solid-State Circuits, **30**:1399–1410, Dezembro.

- Ansari, R. (1987). IIR hilbert transformers, *IEEE* Trans. on Acoustics, Speech and Signal Processing, **35**:1116–1119, Agosto.

- Baruqui, F. A. P., Petraglia, A. e Franca, J. E. (2002). A 48MHz-to-16MHz CMOS SC decimation filter, IEEE J. Solid-State Circuits, 37, Outubro.

- Baschirotto, A., Severi, F. e Castello, R. (2000). A 200-Ms/s 10-mW switched-capacitor filter in 0.5μm CMOS technology, IEEE Journal of Solid-State Circuits, **35**:1215–1219, Agosto.

- Cañive, J. M., Gomes, J. G. R. C. e Petraglia, A. (2000). A CMOS low-sensitivity switched-capacitor video filter, Proc. IEEE Int. Symp. Circuits Syst., Genebra, Suíça, **III**:165–168, Maio.

- Cañive, J. M. e Petraglia, A. (2001). On the testability of SC filters based on allpass sections, *Proc. IEEE Int.* Symp. on Circuits and Systems, Sydney, Austrália, I:65–68, Maio.

- Crols, J. e Stevaert, M. S. J. (1995). A single-chip 900 MHz CMOS receiver front-end with a highperformance low-IF topology, IEEE J. Solid-State Circuits, **30**:1483–1492, Dezembro.

- Gold, B., Oppenheim, A. V. e Rader, C. M. (1970). Theory and implementation of discrete hilbert transform, Proc. IEEE Symp. on Comput. Process. Communication, Polytechnic Press, Brooklyn, N.Y., EUA, pp. 235–250.

- Gomes, J. G. R. C. e Petraglia, A. (2000). A switchedcapacitor DSB to SSB converter using a recursive hilbert transformer with sampling rate reduction, Proc. IEEE Int. Symp. Circuits Syst., Genebra, Suíça, **III**:315–318. Maio.

- Hawley, R. A., Lin, T. e Samueli, H. (1995). A 300 MHz digital double-sideband to single-sideband converter in 1  $\mu$ m CMOS, *IEEE J. Solid-State Circuits*, **30**:4–10, Janeiro.

- Huang, Y., Ferguson, P. e Temes, G. C. (1997). Reduced nonlinear distortion in circuits with correlated double sampling, *IEEE Trans. Circuits Syst. II:*Anal. Dig. Signal Proc., 44:593–597, Julho.

- Jackson, L. B. (1975). On the relationship between digital hilbert transformers and certain low-pass filters, IEEE Trans. on Acoustics, Speech and Signal Processing, pp. 381–383, Agosto.

- Lee, T. H. (1998). The Design of CMOS Radio-Frequency Integrated Circuits, Cambridge University, Reino Unido.

- McNutt, M. J., LeMarquis, S. e Dunkley, J. L. (1994). Systematic capacitance matching errors and corrective layout procedures, *IEEE J. Solid-State Circuits*, **29**:611–616, Maio.

- Mitra, S. K. (2000). Digital Signal Processing A Computer-Based Approach, 2<sup>a</sup> Edição, McGraw-Hill.

- Nagari, A., Raschirotto, A., Montechi, F. e Castello, R. (1997). A 10.7-MHz BiCMOS high-Q doublesampled SC bandpass filter, *IEEE J. Solid-State Circuits*, 32:1491–1498, Outubro.

- Petraglia, A., Barúqui, F. A. P. e Mitra, S. K. (1998). Recursive switched-capacitor hilbert transformers, *IEEE International Symposium on Circuits and* Systems, Monterrey, CA, EUA, I:496–499, Maio.

- Petraglia, A. e Monteiro, M. A. M. (1998). A Switched-Capacitor Filter Having Very Low Sensitivity to Capacitance Ratio Errors and to Finite Amplifier Gains, *IEEE Trans. on Circuits and Systems II:*Analog and Digital Signal Processing, 45(7):890–894, Julho.

- Pun, K. P., Franca, J. E. e Leme, C. A. (1998). Basic principles and new solutions for analog sampleddata image-rejection mixers, *Proc. Int. Conf. Elec*tronics, *Circuits Syst.*, Lisboa, Portugal, III:165– 168, Setembro.

- Rabaey, J. (1996). Digital Integrated Circuits: A Design Perspective, Prentice-Hall.

- Razavi, B. (1998). RF Microelectronics, Prentice-Hall.

- Regalia, P. A. (1993). Special filter designs, *Handbook* for Digital Signal Processing, S. K. Mitra and J. F. Kaiser, Ed. John Wiley & Sons.

- Schüssler, H. W. e Weith, J. (1987). On the design of recursive hilbert-transformers, *Proc. IEEE Inter*national Conference on Acoustics, Speech and Signal Processing, Dallas, TX, EUA, pp. 21.2.1–21.2.4, Abril.

- Schüssler, H. W. (2001). http://www-nt.e-technik.uni-erlangen.de/LNT\_I/LNT\_I.html

- Shyu, J. B., Temes, G. C. e Krummenacher, F. (1984). Random error effects in matched MOS capacitors and current sources. *IEEE J. Solid-State Circuits*, 19:948–955, Dezembro.

- Steyaert, M. e Roovers, R. (1992). A 1-GHz single-chip quadrature modulator, *IEEE J. Solid-State Circuits*, **27**:1194–1197, Agosto.

- Strang, G. e Nguyen, T. (1996). Wavelets and Filter Banks, Wellesley-Cambridge Press.

- Tsui, J. B. Y. (2001). Digital Techniques for Wideband Receivers, 2<sup>a</sup> Edição, Artech House, Norwood, MA, EUA.

- Vaidyanathan, P. P., Regalia, P. A. e Mitra, S. K. (1987). Design of doubly-complementary IIR digital filters using a single complex allpass filter, with multirate applications, *IEEE Trans. Circuits and Systems*, **34**(4):378–389, Abril.

- Web, J. A. e Kelly, M. W. (1978). Delay line helps generate quadrature voice for SSB, *Electronics*, pp. 115–117, 13 de Abril.

- Willingham, S. D. e Martin, K. W. (1990). Effective clock-feedthrough reduction in switched-capacitor circuits *IEEE Int. Symp. on Circuits and Systems*, New Orleans, EUA, pp. 2821–2824.