# UMA METODOLOGIA DE PROJETO GENERALIZADA PARA INVERSORES MULTINÍVEIS HÍBRIDOS

Cassiano Rech\*

cassiano@ieee.org

Hélio L. Hey\*

Hilton A. Gründling\*

Humberto Pinheiro\*

José R. Pinheiro\* renes@ctlab.ufsm.br

\*Grupo de Eletrônica de Potência e Controle, Universidade Federal de Santa Maria, CEP 97105-900 Santa Maria, RS, BRASIL http://www.ufsm.br/gepoc

### **ABSTRACT**

With the use of hybrid multilevel inverters it is possible to reduce the number of series-connected cells for a given number of levels, to minimize the THD of the output voltage and, consequently, to reduce or even eliminate the output filter. Therefore, this paper develops a detailed analysis and proposes a generalized design methodology for hybrid multilevel inverters. With the proposed design methodology it is possible to define the number of series-connected cells, the value of the DC voltage source of each cell, to minimize the circulating energy among the series-connected inverters, and the switching frequency of the lowest power cell.

**KEYWORDS**: Multilevel inverters, high-power high-performance systems, hybrid power conversion systems.

## **RESUMO**

A utilização de inversores multiníveis híbridos possibilita reduzir o número de inversores conectados em série para um determinado número de níveis, minimizar a THD da tensão de saída e, conseqüentemente, reduzir ou

Artigo submetido em 06/08/02 1a. Revisão em 10/12/02

Aceito sob recomendação do Ed. Assoc. Prof. Antonio M. N. Lima

até mesmo eliminar o filtro de saída. Desta forma, este artigo realiza uma análise detalhada e propõe uma metodologia de projeto generalizada para inversores multiníveis híbridos. Com a metodologia de projeto proposta pode-se definir o número de módulos conectados em série, o valor da fonte de tensão de cada módulo, a fim de minimizar a energia circulante entre os inversores conectados em série, e também a freqüência de comutação do módulo de menor potência.

**PALAVRAS-CHAVE**: Inversores multiníveis, sistemas de alta potência e alto desempenho, sistemas de conversão de energia híbridos.

## 1 INTRODUÇÃO

Várias topologias de inversores multiníveis de tensão têm sido desenvolvidas para aplicações de alta potência e de alta tensão (Nabae et alli, 1981; Meynard e Foch, 1992; Lai e Peng, 1996; Hammond, 1997; Suh et alli, 1998). Principalmente, devido à sua capacidade de operar com altos níveis de tensão e potência utilizando dispositivos com baixos limites de tensão, e também ao reduzido conteúdo harmônico das formas de onda de saída, se comparada com as formas de onda obtidas com as topologias dois níveis. Nestas topologias multiníveis, à medida que o número de níveis aumenta, a taxa de

distorção harmônica (THD) da tensão de saída diminui. Entretanto, o número de dispositivos de potência também aumenta, aumentando a complexidade e o custo de todo o sistema.

Por outro lado, inversores multiníveis assimétricos (Damiano et alli, 1997; Manguelle et alli, 2001), que apresentam ao menos uma fonte de tensão com valor diferente das demais fontes, têm sido utilizados para sintetizar formas de onda com maior número de níveis, sem aumentar o número de dispositivos de potência. Entre os inversores multiníveis assimétricos, o inversor multinível em cascata com fontes de tensão de valores diferentes tem sido utilizado, pois não apresenta o problema do desbalanceamento da tensão dos capacitores que compõem o barramento CC, e também devido à sua estrutura modular. Porém, embora a tensão de saída apresente um maior número de níveis, os dispositivos de potência dos diferentes módulos H-bridge (inversor em ponte completa monofásico) são submetidos a níveis de tensão distintos.

Consequentemente, Manjrekar e Lipo (1998) propuseram um inversor multinível híbrido, onde os inversores conectados em série têm as fontes de tensão configuradas na razão 2:1  $(V_{cc}, 2V_{cc}, 4V_{cc}, \dots, 2^{n-1}V_{cc})$ , usam dispositivos de comutação diferentes e também são comandados diferentemente. Esta topologia sintetiza um maior número de níveis com o mesmo número de fontes CC e dispositivos semicondutores do inversor multinível em cascata convencional, e aproveita as vantagens dos diferentes dispositivos de comutação. Lipo e Manjrekar (1999) também generalizaram o conceito de inversores multiníveis híbridos para diferentes topologias de inversores multiníveis e para diferentes configurações de fontes de tensão. Contudo, não é desenvolvida uma metodologia de projeto para definir o número de módulos, os valores das fontes de tensão e as topologias utilizadas em cada módulo.

Assim, este artigo realiza uma análise detalhada e propõe uma metodologia de projeto generalizada para inversores multiníveis híbridos. Com esta topologia é possível minimizar o número de inversores conectados em série para um determinado número de níveis, minimizar a THD da tensão de saída e, consequentemente, reduzir ou até mesmo eliminar o filtro de saída. Com a metodologia de projeto proposta pode-se definir o número de módulos em série, o valor da fonte de tensão de cada módulo, a fim de minimizar a energia circulante entre os inversores, e também a frequência de comutação do módulo de menor potência.

## TOPOLOGIAS BÁSICAS DE INVERSO-**RES MULTINÍVEIS**

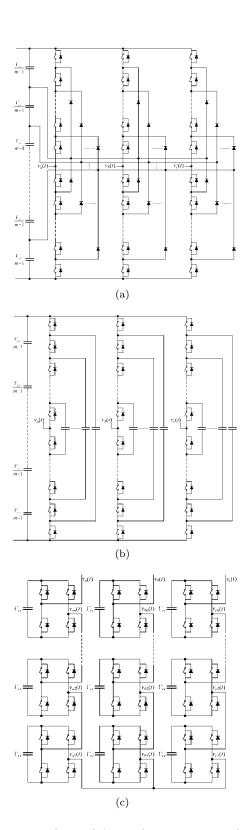

Esta seção apresenta uma breve descrição das topologias básicas de inversores multiníveis propostas na literatura, chamadas: inversor multinível com diodos de grampeamento (diode-clamped multilevel inverter), inversor multinível com capacitores flutuantes (flying-capacitors multilevel inverter) e inversor multinível com módulos H-bridge em cascata (*H-bridge multilevel inverter*).

#### 2.1 Inversor Multinível com Diodos de Grampeamento

O conceito de inversor multinível utilizando diodos de grampeamento foi introduzido por Baker (1980), com a proposta de um inversor três níveis, que foi posteriormente denominado de inversor com ponto neutro grampeado (NPC - Neutral Point Clamped). Além de as tensões de saída apresentarem um menor conteúdo harmônico, esta topologia possibilita a utilização de dispositivos semicondutores com a metade do limite de tensão dos dispositivos utilizados nas topologias dois níveis.

Posteriormente, o inversor NPC foi generalizado para um maior número de níveis, utilizando o mesmo conceito de grampear níveis de tensão com diodos (Baker, 1981; Choi et alli, 1991). A Figura 1(a) mostra um inversor trifásico de m níveis com diodos de grampeamento. Para uma tensão de entrada contínua  $V_{cc}$ , a tensão sobre cada capacitor que compõe o barramento CC é  $V_{cc}/(m-1)$ , e a tensão sobre os interruptores é limitada à tensão de um capacitor do barramento CC.

Entretanto, os diodos de grampeamento devem suportar diferentes níveis de tensão reversa. Assumindo que cada diodo de grampeamento possui a mesma especificação de tensão dos interruptores, o número de diodos de grampeamento cresce rapidamente e é igual a 3(m-1)(m-2), conforme apresentado na Tabela 1, que mostra uma comparação do número de dispositivos de potência utilizados nas topologias básicas de inversores multiníveis (Lai e Peng, 1996). É importante ressaltar que nesta comparação não são incluídos os componentes requeridos para implementar as fontes de tensão, que são necessárias em aplicações com transferência de potência ativa.

Ainda, nestas aplicações com transferência de potência ativa, deve-se também evitar o desbalanceamento das tensões dos capacitores que compõem o barramento CC (Celanovic e Boroyevich, 1999).

Figura 1: Topologias básicas de inversores multiníveis. (a) Com diodos de grampeamento. (b) Com capacitores flutuantes. (c) Módulos H-bridge em cascata.

#### 2.2 Inversor Multinível com Capacitores **Flutuantes**

Outra topologia, que utiliza capacitores para grampear a tensão sobre os interruptores ao invés de diodos de grampeamento, é mostrada na Figura 1(b) e é usualmente chamada de inversor multinível com capacitores flutuantes (Meynard e Foch, 1992).

Ao contrário da topologia mostrada na Figura 1(a), o inversor multinível com capacitores flutuantes possui estados de comutação redundantes para sintetizar a tensão de fase, ou seja, alguns valores da tensão de fase podem ser sintetizados por mais de um estado de comutação.

Contudo, além da dificuldade do desbalanceamento da tensão dos capacitores em aplicações com transferência de potência ativa, o maior problema desta topologia é a necessidade de um grande número de capacitores. Para que cada capacitor esteja sujeito à mesma especificação de tensão dos interruptores principais torna-se necessário a utilização de capacitores em série. Portanto, são necessários 3(m-1)(m-2)/2 capacitores de grampeamento, além de (m-1) capacitores do barramento CC.

### 2.3 Inversor Multinível com Módulos H-bridge em cascata

A conexão de módulos monofásicos em série para sintetizar formas de onda de tensão multiníveis foi apresentada pela primeira vez por Baker e Bannister (1975). Nesta patente norte-americana, vários inversores monofásicos em ponte completa (inversores H-bridge) são conectados em série para obter uma tensão de saída com uma forma de onda quase senoidal. A Figura 1(c) mostra a estrutura de um inversor multinível trifásico conectado em Y com n módulos H-bridge em cascata. Esta topologia tem sido utilizada em aplicações de alta potência, como, por exemplo, na compensação estática de reativos (Joos et alli, 1998), porque não requer a utilização de diodos e/ou capacitores de grampeamento, e também porque não ocorre o problema de desbalanceamento das fontes de tensão. Uma tensão de fase de saída é obtida somando-se a tensão de saída de cada módulo, por exemplo:

$$v_a(t) = v_{a1}(t) + v_{a2}(t) + \dots + v_{an}(t)$$

(1)

Se as fontes de tensão de todos os módulos H-bridge são iguais, então o número de níveis é dado por:

$$m = 1 + 2n \tag{2}$$

| ш | inparação do número de dispositivos utilizados has topologias basicas de niverso |              |               |                  |

|---|----------------------------------------------------------------------------------|--------------|---------------|------------------|

|   | Tipo de                                                                          | Diodos de    | Capacitores   | Módulos H-bridge |

|   | inversor                                                                         | grampeamento | flutuantes    | em cascata       |

|   | Chaves                                                                           | 6(m-1)       | 6(m-1)        | 6(m-1)           |

|   | principais                                                                       |              |               |                  |

|   | Diodos                                                                           | 6(m-1)       | 6(m-1)        | 6(m-1)           |

|   | principais                                                                       |              |               |                  |

|   | Diodos de                                                                        | 3(m-1)(m-2)  | 0             | 0                |

|   | grampeamento                                                                     |              |               |                  |

|   | Capacitores do                                                                   | (m-1)        | (m-1)         | 1.5(m-1)         |

|   | barramento CC                                                                    |              |               |                  |

|   | Capacitores de                                                                   | 0            | 1.5(m-1)(m-2) | 0                |

|   | grampeamento                                                                     |              |               |                  |

Tabela 1: Comparação do número de dispositivos utilizados nas topologias básicas de inversores multiníveis.

## DESCRIÇÃO DOS INVERSORES MUL-TINÍVEIS HÍBRIDOS

A partir da Tabela 1 verifica-se que o inversor multinível com módulos H-bridge em série apresenta o menor número de componentes entre as topologias convencionais. Entretanto, vários módulos devem ser conectados em série para obter um maior número de níveis, aumentando a complexidade e o custo de todo sistema.

Assim, inversores multiníveis assimétricos (Damiano et alli, 1997; Manguelle et alli, 2001), que apresentam ao menos uma fonte de tensão com valor diferente das demais fontes, têm sido utilizados para sintetizar tensões de saída com um maior número de níveis, sem aumentar o número de dispositivos de potência.

Então, considerando que a menor fonte de tensão de todos os módulos H-bridge é escolhida como valor base de tensão para a normalização, os valores normalizados de todas as fontes de tensão devem ser números naturais (reais inteiros positivos) para sintetizar formas de onda com degraus de tensão uniformes, isto é:

$$V_j \in \mathbb{N}, \quad j = 1, 2, ..., n \tag{3}$$

Ainda, para obter formas de onda com degraus de tensão uniformes, os valores normalizados de todas as fontes de tensão devem respeitar (4) (Manguelle et alli, 2001):

$$V_j \le 1 + 2 \sum_{k=1}^{j-1} V_k, \quad j = 2, 3, \dots, n$$

(4)

onde também se considera que as fontes de tensão estão arranjadas em uma forma crescente, ou seja:

$$V_1 \le V_2 \le V_3 \le \dots \le V_n \tag{5}$$

Se (3) e (4) são respeitadas, o número de níveis do inversor multinível assimétrico é dado por:

$$m = 1 + 2\,\sigma_n\tag{6}$$

sendo:

$$\sigma_n = \sum_{j=1}^n V_j \tag{7}$$

Desta forma, a partir de (2) e (6)-(7) verifica-se que os inversores multiníveis assimétricos podem gerar um maior número de níveis com um mesmo número de módulos H-bridge.

Entretanto, como são utilizadas fontes de tensão com valores diferentes, os dispositivos de potência dos diferentes módulos são submetidos a níveis de tensão distintos. Então, pode-se tornar necessário empregar dispositivos com capacidade para bloquear altos níveis de tensão, tais como GTO's e IGCT's, nos módulos com uma fonte de tensão de valor elevado. Contudo, sabe-se que estes dispositivos não operam adequadamente com altas frequências de comutação. Por outro lado, dispositivos rápidos, tais como IGBT's e MOSFET's, não podem ser submetidos a altos níveis de tensão.

Assim, Manjrekar e Lipo (1998) propuseram um inversor multinível híbrido para aplicações de alta potência e alta performance. Este inversor combina dispositivos rápidos (IGBT's) com componentes capazes de operar com altos níveis de tensão (GTO's). Estes dispositivos são modulados diferentemente, tal que o inversor com GTO's (maior potência) é modulado na frequência fundamental da saída e o inversor com IGBT's (menor potência) é modulado em alta frequência.

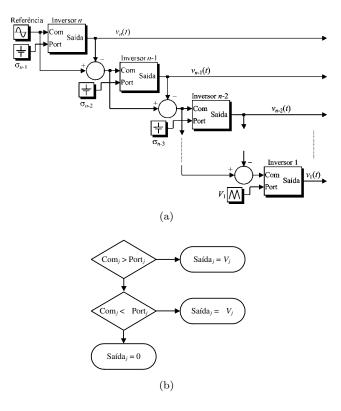

## 3.1 Estratégia de Modulação

Lipo e Manjrekar (1999) apresentaram uma estratégia de modulação que associa a síntese de formas de onda quase-quadradas para os inversores de maior potência juntamente com modulação por largura de pulso (PWM) para o inversor de menor potência.

Porém, para sintetizar uma forma de onda de tensão modulada em alta freqüência entre todos os degraus de tensão adjacentes, comutando em alta freqüência somente o inversor de menor potência, as fontes de tensão devem respeitar a seguinte equação (Rech et alli, 2002):

$$V_j \le 2 \sum_{k=1}^{j-1} V_k, \quad j = 2, 3, ..., n$$

(8)

Assim, se (8) é satisfeita, as harmônicas da tensão de saída estarão concentradas em torno de freqüências múltiplas da freqüência de comutação do inversor de menor potência. Logo, com esta topologia e esta estratégia de modulação, o conteúdo harmônico da tensão de saída do inversor multinível depende da freqüência de comutação do inversor de menor potência, enquanto que o processamento de potência depende basicamente do inversor com a maior fonte de tensão.

A Figura 2 mostra um esquema do circuito utilizado para determinar os sinais de comando dos interruptores do inversor multinível híbrido. A Figura 2(a) mostra que o sinal de referência do inversor multinível também é o sinal de comando do módulo com a maior fonte de tensão. Este sinal é comparado com um nível de tensão correspondente à soma de todas as fontes de tensão dos inversores de menor potência  $(\sigma_{n-1})$ . Como mostrado na Figura 2(b), se o sinal de comando for maior que este nível, a saída do inversor de maior potência deve ser igual à  $V_n$ . Se o sinal de comando for menor que o valor negativo de  $\sigma_{n-1}$ , a saída deste inversor será igual a  $V_n$ . Por outro lado, se nenhuma destas condições for satisfeita a saída deste inversor será igual a zero.

O sinal de comando do j-ésimo inversor é a diferença entre o sinal de comando e a tensão de saída do inversor j+1. Este sinal de comando é comparado com um nível de tensão correspondente à soma de todas as fontes de tensão até o inversor j-1 ( $\sigma_{j-1}$ ). Da mesma forma que para o inversor n, a tensão de saída do módulo é gerada a partir da comparação destes dois sinais (Figura 2(b)). Já o sinal de comando do primeiro inversor (menor potência) é comparado com uma forma de onda triangular de amplitude  $V_1$  e freqüência  $f_s$ , resultando em uma tensão de saída modulada em alta freqüência. Assim, o índice de modulação de freqüência  $m_f$  do in-

Figura 2: Estratégia de modulação para inversores multiníveis híbridos.

versor multinível híbrido é definido como a razão entre a freqüência de comutação do inversor de menor potência e a freqüência do sinal de referência.

### 4 METODOLOGIA DE PROJETO

Nesta seção é proposta uma nova metodologia de projeto generalizada para inversores multiníveis híbridos. Com esta metodologia garante-se que o processamento de potência depende basicamente do inversor com a maior fonte de tensão e que a energia circulante entre os inversores é minimizada para toda faixa de valores de índice de modulação de amplitude  $(m_a)$ .

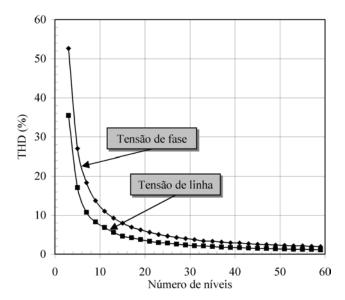

## 4.1 Número de Níveis

Na Figura 3 é mostrada a THD das tensões de saída do inversor multinível, sem filtro de saída, em função do número de níveis, considerando um índice de modulação de amplitude unitário ( $m_a=1$ ). Este gráfico foi obtido empregando uma estratégia de modulação com múltiplas portadoras, onde todas as portadoras estão em fase ( $Phase\ Disposition\ -\ PD$ ). Com esta disposição das portadoras, a harmônica mais significativa está concentrada na frequência da portadora, contudo esta

Figura 3: THD x Número de níveis.

componente não aparece nas tensões de linha (Agelidis e Calais, 1998). Assim, as tensões de linha apresentam uma menor THD.

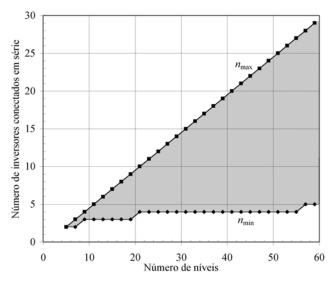

Embora o número de níveis possa ser determinado a partir da especificação da THD da tensão de saída, existem inúmeras possibilidades para obter o mesmo número de níveis. O número necessário de módulos H-bridge em série para gerar um determinado número de níveis será mínimo  $(n_{min})$  quando:

$$V_j = 2 \sum_{k=1}^{j-1} V_k, \quad j = 2, 3, \dots, n$$

(9)

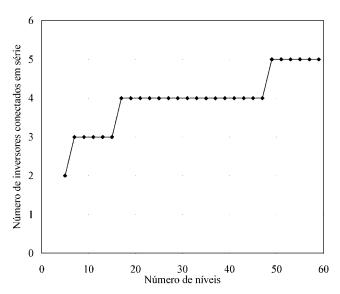

Por outro lado, o número necessário de módulos Hbridge para gerar um determinado número de níveis será máximo  $(n_{max})$  quando as fontes de tensão de todos os módulos H-bridge possuirem o mesmo valor. Logo, a Figura 4 mostra que uma forma de onda com m níveis pode ser obtida a partir de diferentes números de inversores em série, principalmente à medida que o número de níveis aumenta.

#### 4.2 Valor da Fonte de Tensão do Inversor de Maior Potência

Assumindo que a corrente de saída é senoidal, então a corrente de saída normalizada  $i_o(t)$  pode ser representada por:

$$i_o(t) = \sqrt{2}I_o sen(\omega t + \beta_1) \tag{10}$$

Figura 4: Número mínimo e máximo de módulos Hbridge em série.

onde  $\beta_1$  é o ângulo de fase da corrente e  $I_o$  é o valor eficaz normalizado da corrente de saída.

Ainda, uma tensão de fase de saída normalizada do inversor multinível pode ser representada por:

$$v_o(t) = \sqrt{2} \sum_{k=1}^{\infty} V_{ok} sen(k\omega t + \alpha_k)$$

(11)

onde  $V_{ok}$  é o valor eficaz normalizado e  $\alpha_k$  é o ângulo de fase da k-ésima harmônica da tensão de fase.

Assim, a potência total ou aparente normalizada de uma fase do inversor multinível pode ser dada pela soma de duas componentes:

$$S_o^2 = (V_{RMS}I_o)^2 = S_{o1}^2 + S_{oh}^2$$

(12)

onde:

$$V_{RMS} = \sqrt{\sum_{k=1}^{\infty} \left(V_{ok}\right)^2},\tag{13}$$

$$S_{o1} = V_{o1}I_o, \quad S_{oh} = V_{oh}I_o,$$

(14)

$$V_{oh}^{2} = \sum_{k=2}^{\infty} (V_{ok})^{2}$$

(15)

Aqui,  $S_{o1}$  é chamada de potência aparente fundamental, e  $S_{oh}$  pode ser chamada de potência aparente nãofundamental (IEEE Working Group on Nonsinusoidal Situations, 1996).

Por outro lado, a tensão de saída normalizada do j-ésimo módulo H-bridge  $v_i(t)$  pode ser dada por:

$$v_j(t) = \sqrt{2} \sum_{k=1}^{\infty} V_{jk} sen(k\omega t + \alpha_{jk})$$

(16)

onde  $V_{jk}$  é o valor eficaz normalizado e  $\alpha_{jk}$  é o ângulo de fase da k-ésima harmônica da tensão de saída do j-ésimo inversor.

Logo, a potência aparente normalizada processada por cada módulo é dada por:

$$S_i^2 = (V_{RMS_i}I_o)^2 = S_{i1}^2 + S_{ih}^2$$

(17)

onde  $V_{RMSj}$  é o valor eficaz normalizado da tensão de saída do j-ésimo inversor e:

$$S_{j1} = V_{j1}I_o, \quad S_{jh} = V_{jh}I_o$$

(18)

Assumindo que as tensões de referência do inversor multinível híbrido são senoidais, a maior parte da potência ativa que flui pelo sistema é potência ativa fundamental. Assim, torna-se importante analisar a quantidade da potência aparente fundamental processada por cada módulo, especialmente pelo módulo com a maior fonte de tensão.

O princípio básico dos inversores multiníveis híbridos é que o módulo com a maior fonte de tensão deve processar a maior quantidade possível de potência, sem exceder a potência drenada pela carga, enquanto que o módulo com a menor fonte de tensão deve melhorar o desempenho harmônico do inversor multinível híbrido. Desta forma, é importante verificar o valor máximo da fonte de tensão do módulo H-bridge de maior potência, tal que este inversor não processe mais potência aparente fundamental do que necessário.

Se o módulo com a maior fonte de tensão (n-ésimo inversor) não processa mais potência aparente fundamental do que a quantidade drenada pela carga, então:

$$S_{n1} < S_{o1}$$

(19)

Logo, a partir de (14) e (18), obtém-se que:

$$V_{n1} \le V_{o1} \tag{20}$$

Portanto, se (20) é satisfeita, o módulo de maior potência não processará mais potência aparente fundamental que necessário, independentemente do valor da corrente de carga.

Assim, de acordo com (8), pode-se assumir que:

$$V_n = K \sum_{k=1}^{n-1} V_k, \quad K \le 2$$

(21)

Desta forma, como o inversor de maior potência é comutado na freqüência fundamental, o valor eficaz normalizado da componente fundamental da tensão de saída deste inversor pode ser dado por:

$$V_{n1} = \frac{2\sqrt{2}K\sigma_n}{\pi (1+K)} \cos\left[sen^{-1}\left(\frac{1}{m_a(1+K)}\right)\right]$$

(22)

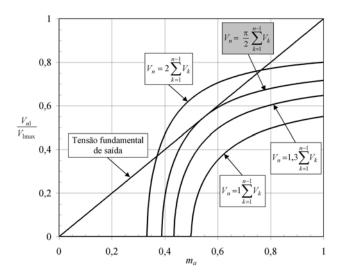

A Figura 5 mostra a razão da componente fundamental de tensão sintetizada pelo inversor de maior potência pela componente fundamental da tensão de saída com índice de modulação unitário  $(V_{1max})$ , para diferentes valores de K. Pode-se observar que o inversor de maior potência sintetiza mais componente fundamental de tensão do que necessário para valores de  $m_a$  entre 0,37 e 0,77, quando a máxima fonte de tensão permitida é utilizada (K=2). Este excesso de tensão resulta em uma energia circulante entre os inversores, reduzindo a eficiência do sistema.

A partir da Figura 5 também verifica-se que o inversor de maior potência sintetiza a maior componente fundamental de tensão, sem excesso, quando:

$$V_n = \frac{\pi}{2} \sum_{k=1}^{n-1} V_k \tag{23}$$

Então, utilizando (6) e (7), pode-se obter o valor normalizado da fonte de tensão do inversor de maior potência em função do número de níveis, dado por:

$$V_n = floor \left[ \frac{\pi}{2(\pi + 2)} (m - 1) \right]$$

(24)

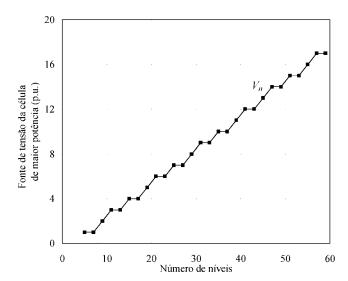

onde floor[...] é uma relação que transforma seu argumento (pertencente ao conjunto dos números reais) para o número natural imediatamente anterior. A Figura 6 mostra o gráfico que relaciona a fonte de tensão normalizada do inversor de maior potência em função do número de níveis do inversor multinível.

# 4.3 Número de Módulos H-bridge Conectados em Série

Com a escolha adequada da fonte de tensão do inversor de maior potência garante-se que este módulo não processará mais potência do que a quantidade drenada

Figura 5: Componente fundamental de tensão sintetizada pelo inversor de maior potência para diferentes valores de fontes de tensão.

Figura 6: Valor normalizado da fonte de tensão do inversor de maior potência.

pela carga. O número de módulos H-bridge em série pode então ser definido para que seja o número mínimo de módulos que produzam o número de níveis necessário. Mesmo se algum inversor de menor potência processar mais potência do que necessário isto ocorrerá para baixos valores de  $m_a$  e o seu valor não será significativo se comparado com a potência nominal processada pelo módulo com a maior fonte de tensão.

Então, considerando que todas as fontes de tensão, com exceção da fonte do inversor de maior potência, são ob-

Figura 7: Número de módulos H-bridge conectados em série.

tidas a partir de (9) (número mínimo de módulos), o somatório dos valores destas fontes é dado por:

$$\sigma_{n-1} = 3^{n-2} \tag{25}$$

Como  $\sigma_n = V_n + \sigma_{n-1}$  é possível demonstrar que:

$$n = ceil \left[ 2 + \log_3 \left( \frac{m-1}{2} - V_n \right) \right] \tag{26}$$

onde ceil[...] é uma relação que transforma seu argumento para o número natural imediatamente posterior.

A Figura 7 mostra o gráfico que relaciona o número de módulos H-bridge em série com o número de níveis do inversor multinível híbrido. Com este número de módulos é possível gerar o número de níveis desejado, sem que o inversor com a maior fonte de tensão processe potência em excesso e, além disso, é possível modular em alta fregüência a forma de onda da tensão de saída entre todos degraus de tensão adjacentes.

#### Valores das Fontes de Tensão dos Mó-4.4 dulos de Menor Potência

Além de o inversor com a maior fonte de tensão não processar mais potência do que necessário, os módulos H-bridge restantes também podem ser projetados para que não processem potência em excesso ou para que este excesso seja o menor possível.

Com a estratégia de modulação híbrida utilizada, quando um módulo está comutando na frequência fundamental da tensão de saída, o mesmo poderá processar mais potência do que a quantidade drenada pela carga. Mas, de acordo com (23), pode-se verificar que o j-ésimo inversor H-bridge não processará mais potência do que a quantidade drenada pela carga se:

$$V_j = \frac{\pi}{2} \sum_{k=1}^{j-1} V_k \tag{27}$$

Além disso, considerando que os valores das fontes de tensão dos outros inversores de menor potência são definidos a partir de (9), pode-se obter que:

$$\sigma_j = \frac{\pi + 2}{2} \left( 3^{j-2} \right) \tag{28}$$

Assim, se o somatório de tensões desejado para os j primeiros inversores for menor ou igual que (28), o j-ésimo inversor não precisará processar potência em excesso. Por outro lado, se o somatório das tensões desejado para os inversores restantes for maior que (28), o j-ésimo inversor precisará processar mais potência do que necessário. Então, o valor normalizado da fonte de tensão do j-ésimo módulo pode ser obtido por:

$$V_{j} = \begin{cases} floor\left(\frac{\pi}{\pi+2}\sigma_{j}\right), & \sigma_{n} - \sum_{i=j+1}^{n} V_{i} \leq \frac{\pi+2}{2} \left(3^{j-2}\right) \\ ceil\left(\frac{\pi}{\pi+2}\sigma_{j}\right), & \sigma_{n} - \sum_{i=j+1}^{n} V_{i} > \frac{\pi+2}{2} \left(3^{j-2}\right) \end{cases}$$

$$(29)$$

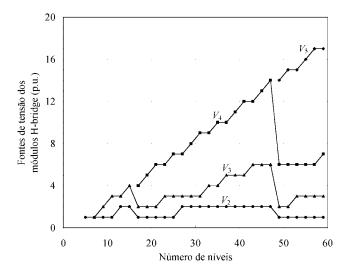

A Figura 8 apresenta os valores normalizados das fontes de tensão dos inversores, obtidos a partir de (29), em função do número de níveis.

# 4.5 Freqüência de Comutação do Módulo de Menor Potência

Ao se aplicar modulação por largura de pulso, deseja-se controlar o valor médio da variável de interesse em um intervalo de tempo. No caso de inversores multiníveis, a freqüência de comutação do inversor pode ser determinada para que o erro entre o valor médio da tensão de saída entre dois degraus de tensão adjacentes e o valor médio da tensão de referência neste mesmo intervalo de tempo seja mínimo.

Então, definindo que o erro percentual entre o valor médio da tensão de referência  $(\bar{v}_{ref})$  e o valor médio da tensão de fase  $(\bar{v}_o)$  entre dois degraus de tensão adjacentes é dado por:

$$e_{med} = \frac{\bar{v}_{ref} - \bar{v}_o}{\sigma_n} \, 100(\%) \tag{30}$$

Figura 8: Valores normalizados das fontes de tensão dos módulos H-bridge.

Figura 9: Índice de modulação de frequência do módulo de menor potência.

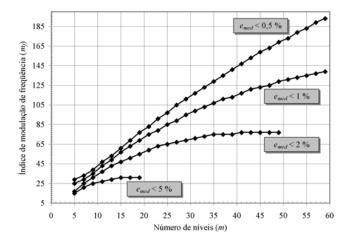

O índice de modulação de freqüência mínimo do módulo de menor potência que garante que o erro percentual entre o valor médio da tensão de referência e o valor médio da tensão de fase entre todos os degraus de tensão adjacentes é menor que o valor especificado é mostrado na Figura 9, em função do número de níveis.

# 5 RESULTADOS DE SIMULAÇÃO

Como exemplo de projeto, considera-se que a THD da tensão de fase de saída, sem filtro de saída, deve ser menor que 5% para um índice de modulação de amplitude unitário. A partir da Figura 3 pode-se observar que se o número de níveis for igual a 25, a THD da tensão de fase ficará em torno de 5%. Então, da Figura 7 pode-se

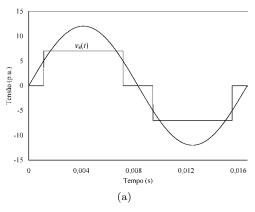

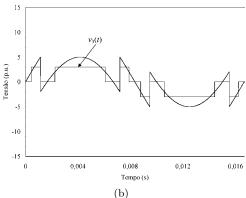

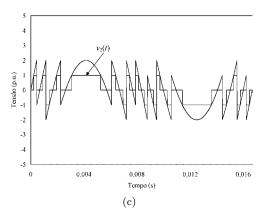

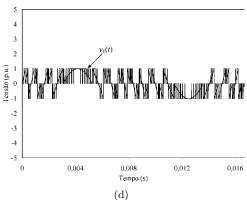

Figura 10: Tensão dos inversores. (a) Inversor 4 (maior potência). (b) Inversor 3. (c) Inversor 2. (d) Inversor 1 (menor potência).  $m_a = 1$ ,  $m_f = 97$ .

| Tabela 2: Parâmetros do sistema. |                        |                        |  |  |

|----------------------------------|------------------------|------------------------|--|--|

| Parâmetro                        | Valor                  |                        |  |  |

| Número de                        | 25                     |                        |  |  |

| níveis $(m)$                     |                        |                        |  |  |

| Número de inversores             | 4                      |                        |  |  |

| em série $(n)$                   |                        |                        |  |  |

| Fontes de tensão                 | $V_1 = 1 \text{ p.u.}$ | $V_3 = 3 \text{ p.u.}$ |  |  |

| normalizadas $(V_j)$             | $V_2 = 1 \text{ p.u.}$ | $V_4 = 7 \text{ p.u.}$ |  |  |

| Índice de modulação              | 97                     |                        |  |  |

| de frequência $(m_f)$            |                        |                        |  |  |

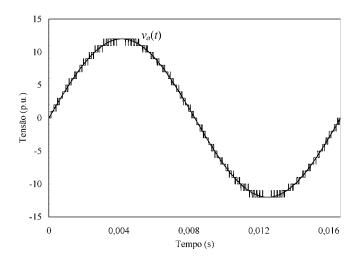

Figura 11: Tensão de fase do inversor multinível híbrido.

obter o número de módulos H-bridge que devem ser conectados em série, e da Figura 8 pode-se definir os valores normalizados das fontes de tensão dos respectivos módulos. Finalmente, o índice de modulação de freqüência do módulo de menor potência pode ser obtido a partir da Figura 9, considerando, por exemplo, que o erro médio deve ser menor que 0,5 %. Os parâmetros obtidos a partir da metodologia de projeto são apresentados na Tabela 2.

Assim, a partir dos dados da Tabela 2 realizou-se a simulação de um inversor multinível híbrido, a fim de validar a metodologia de projeto proposta. Na Figura 10 são mostradas as formas de onda da tensão de saída e de referência de cada módulo, utilizando um índice de modulação de amplitude unitário. A Figura 11 mostra a tensão de referência e a tensão de fase obtida a partir da soma das tensões de saída dos 4 inversores H-bridge em série.

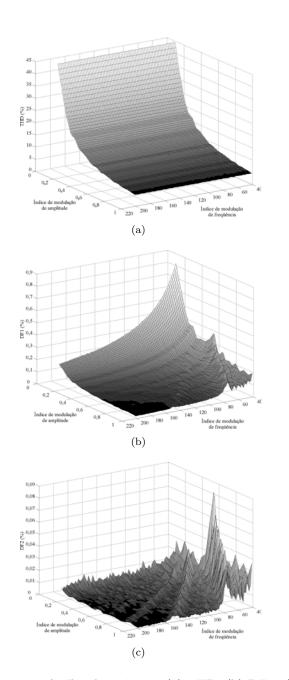

A Figura 12 mostra a THD e os fatores de distorção de primeira ordem (DF1) e de segunda ordem (DF2) da tensão de fase em função de  $m_a$  e de  $m_f$ , para verificar o desempenho harmônico deste inversor híbrido. Em-

Figura 12: Análise harmônica. (a) THD. (b) DF1. (c) DF2.

bora a THD não dependa de  $m_f$ , conforme mostrado na Figura 12(a), os índices DF1 e DF2 dependem do valor de  $m_f$ , como pode ser visto na Figura 12(b) e na Figura 12(c). É possível constatar que para valores de  $m_f$  maiores que 100 não ocorre uma grande diminuição nos valores de DF1 e DF2.

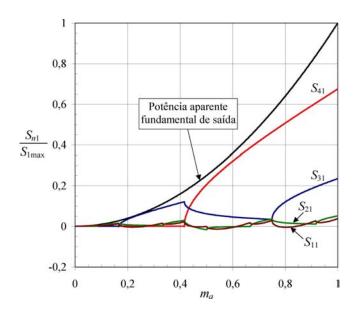

A Figura 13 mostra a potência aparente fundamental processada pelos módulos H-bridge em função da variação de  $m_a$ , para uma carga linear. Pode-se comprovar

Figura 13: Potência aparente fundamental processada pelos módulos H-bridge.

que o módulo de maior potência processa a maior quantidade de potência, sem exceder a potência drenada pela carga.

# 6 CONCLUSÕES

Este trabalho apresenta uma análise detalhada e propõe uma nova metodologia de projeto generalizada para inversores multiníveis híbridos. Com inversores multiníveis híbridos, um maior número de níveis pode ser obtido com o mesmo número de dispositivos de potência do inversor multinível em cascata convencional, possibilitando reduzir ou até mesmo eliminar o filtro de saída. Com a metodologia de projeto proposta pode-se definir o número de módulos conectados em série e a fonte de tensão de cada módulo, a fim de minimizar a energia circulante entre os inversores e, conseqüentemente, aumentar a eficiência de todo sistema. Além disso, também pode-se definir a freqüência de comutação do módulo de menor potência.

## **REFERÊNCIAS**

Agelidis, V. G., Calais, M. (1998). Application Specific Harmonic Performance Evaluation of Multicarrier PWM Techniques. *IEEE PESC Conf. Rec.*, (1): 172-178.

Baker, R. H. (1980). Switching Circuit. U. S. Patent 4 210 826, Estados Unidos.

- Baker, R. H. (1981). Bridge Converter Circuit. U. S. Patent 4 270 163, Estados Unidos.

- Baker, R. H., Bannister, L. H. (1975). Electric Power Converter. U. S. Patent 3 867 643, Estados Unidos.

- Celanovic, N., Boroyevich, D. (1999). A Comprehensive Study of Neutral-Point Voltage Balancing Problem in Three-Level Neutral-Point-Clamped Voltage Source PWM Inverters. *Proc. IEEE APEC'99*: 535–541.

- Choi, N. S., Cho, J. G., Cho, G. H. (1991). A General Circuit Topology of Multilevel Inverter. *IEEE PESC Conf. Rec.*, (1): 96-103.

- Damiano, A., Marchesoni, M., Marongiu, I., Taffone, A. (1997). Optimization of Harmonic Performances in Multilevel Converter Structures. ISIE Conf. Proc.: pp. 341–346.

- Hammond, P. W. (1997). Medium Voltage PWM Drive and Method. U. S. Patent 5 625 545, Estados Unidos.

- IEEE Working Group on Nonsinusoidal Situations (1996). Practical Definitions for Powers in Systems with Nonsinusoidal Waveforms and Unbalanced Loads: A Discussion. *IEEE Trans. Power Deliv.*, 11(1): 79–101.

- Joos, G., Huang, X., Ooi, B.-T. (1998). Direct-Coupled Multilevel Cascaded Series Var Compensators. *IEEE Trans. Ind. Applicat.*, 34(5): 1156–1163.

- Lai, J. S., Peng, F. Z. (1996). Multilevel Converters A New Breed of Power Converters. *IEEE Trans. Ind. Applicat.*, 32(3): 509–517.

- Lipo, T. A., Manjrekar, M. D. (1999). Hybrid Topology for Multilevel Power Conversion. U. S. Patent 6 005 788, Estados Unidos.

- Manguelle, J. S., Mariethoz, S., Veenstra, M., Rufer, A. (2001). A Generalized Design Principle of a Uniform Step Asymmetrical Multilevel Converter for High Power Conversion. *EPE Conf. Rec.*.

- Manjrekar, M. D., Lipo, T. A. (1998). A Hybrid Multilevel Inverter Topology for Drive Applications. *Proc. IEEE APEC'98*: 523–529.

- Meynard, T. A., Foch, H. (1992). Multi-Level Conversion: High Voltage Choppers and Voltage-Source Inverters. *IEEE PESC Conf. Rec.*: 397-403.

- Nabae, A., Takahashi, I., Akagi, H. (1981). A New Neutral-Point-Clamped PWM Inverter. *IEEE Trans. Ind. Applicat.*, 17(5): 518–523.

- Rech, C., Pinheiro, H., Gründling, H. A., Hey, H. L., Pinheiro, J. R. (2002). Analysis and Comparison of Hybrid Multilevel Voltage Source Inverters. *IEEE PESC Conf. Rec.*, (2): 491–496.

- Suh, B. S., Sinha, G., Manjrekar, M. D., Lipo, T. A. (1998). Multilevel Power Conversion An Overview of Topologies and Modulation Strategies. *Proc. OP-TIM'98*: AD-11-AD-24.