# BEAMFORMER DE TRANSMISSÃO MULTICANAL DE FORMA DE ONDA ARBITRÁRIA PARA ATIVIDADES DE PESQUISA EXPERIMENTAL DO ULTRASSOM

Amauri A. Assef\*

amauriassef@utfpr.edu.br

Fábio K. Schneider\*

fabioks@utfpr.edu.br

Vera L. da S. N. Button<sup>†</sup>

vera@ceb.unicamp.br

\*Universidade Tecnológica Federal do Paraná - UTFPR Programa de Pós-Graduação em Engenharia Elétrica e Informática Industrial - CPGEI Av. Sete de Setembro, 3165 - Rebouças 80230-901, Curitiba, Paraná, Brasil

> <sup>†</sup>Universidade Estadual de Campinas - UNICAMP Departamento de Engenharia Biomédica - DEB, Faculdade de Engenharia Elétrica e de Computação - FEEC Centro de Engenharia Biomédica - CEB Caixa Postal 6040 13084-971, Campinas, São Paulo, Brasil

#### **ABSTRACT**

### Multichannel Arbitrary Waveform Beamformer Transmitter for Experimental Research Activities of Ultrasound

This paper presents the development of a digital beamformer transmitter system for generation of arbitrary ultrasound waveforms, specifically designed for research purposes. The proposed architecture has 8 independent excitation channels and uses an FPGA device (Field Programmable Gated Array) for electronic control channel generation of ultrasonic acoustic beam transmission. The system allows operation in pulse-echo mode, with pulse repetition rate of excitation between 62.5 Hz and 8 kHz, or single pulse, center frequency between 500 kHz and 20 MHz, excitation voltage between

apodization, phase angle and time delay trigger. The mathematical method for determining the digital signals of excitation is presented and validated through practical results for waveform generation with Gaussian profile and center frequency of 20 MHz, in a load formed by a 220 pF capacitor in parallel with a resistor of 1 k $\Omega$ . The results show that the proposed flexible and fully programmable architecture, can support the development of new algorithms and sophisticated processing techniques of the transmission beamformer.

-100 and +100 V, and individual control of amplitude

Joaquim M. Maia\*

joaquim@utfpr.edu.br

Eduardo T. Costa<sup>†</sup>

educosta@ceb.unicamp.br

**KEYWORDS**: Ultrasound, beamformer transmitter, arbitrary waveform, FPGA.

### **RESUMO**

Este trabalho apresenta o desenvolvimento de um sistema digital beamformer de transmissão para geração de formas de

Artigo submetido em 19/10/2011 (Id.: 1388) Revisado em 13/01/2012, 27/01/2012 Aceito sob recomendação do Editor Associado Prof. Takashi Yoneyama onda arbitrárias de ultrassom, projetado especificamente para fins de pesquisa. A arquitetura proposta possui 8 canais de excitação independentes e utiliza um dispositivo FPGA (Field Programmable Gated Array) para controle eletrônico dos canais de geração do feixe acústico ultrassônico de transmissão. O sistema permite operação no modo pulso-eco, com taxa de repetição dos pulsos de excitação entre 62,5 Hz e 8 kHz, ou pulso único, frequência central entre 500 kHz e 20 MHz, tensão de excitação entre -100 V e +100 V, e controle individual da amplitude de apodização, ângulo de fase e atraso temporal de disparo. O método matemático para determinação dos sinais digitais de excitação é apresentado e validado através dos resultados práticos para geração de forma de onda com perfil Gaussiano e frequência central de 20 MHz, em uma carga equivalente formada por um capacitor de 220 pF em paralelo com um resistor de 1 k $\Omega$ . Os resultados demonstram que a arquitetura flexível e totalmente programável proposta, pode apoiar o desenvolvimento de novos algoritmos e técnicas sofisticadas de processamento do beamformer de transmissão.

PALAVRAS-CHAVE: Ultrassom, beamformer de transmissão, forma de onda arbitrária, FPGA.

## INTRODUÇÃO

O avanço na tecnologia dos transdutores e o desenvolvimento de equipamentos para geração de imagens médicas por ultrassom (US) mais flexíveis e com alta capacidade de processamento digital de sinais, representam importantes fatores que poderão impactar diretamente sobre o sucesso da técnica para novas modalidades de imagens em tempo real, melhorando a capacidade de diagnóstico (Basoglu et al., 1998; Mahdy et al., 2006). Para tal, são necessárias pesquisas em plataformas de hardware reconfiguráveis com capacidade de atualização contínua de funcionalidades (Silkdar et al., 2003; Jensen et al., 2005; Schneider et al., 2010), como por exemplo, controle programável de formação do feixe acústico de US com diferentes modos de excitação (Kim et al., 1997; Park et al., 2010).

Atualmente, grande parte dos transdutores de US desenvolvidos para aplicações clínicas especificas, tais como, cardiologia, radiologia, obstetrícia e endoscopia, utilizam a tecnologia phased array, podendo conter centenas de elementos piezoelétricos (Ricci et al., 2007). Estes elementos são arranjados matricialmente (1D e 2D) e apresentam grande largura de banda, ou seja, podem operar em diferentes frequências (Olympus NDT, 2007). Assim, circuitos de transmissão com capacidade de excitação independente e com defasagem temporal em cada elemento piezoelétrico, compõem um item fundamental para o aprimoramento na formação de imagens médicas por US, através da aplicação de técnicas sofisticadas de processamento de sinais (Tomov & Jensen, 2005), como compressão de pulso (Misaridis & Jensen, 2005) ou focalização eletrônica e dinâmica (Zhou & Hossack, 2003; Park et al., 2010), além da geração de forma de onda arbitrária utilizando diferentes modulações (Huang & Li, 2006).

Trabalhos recentes (Ricci et al., 2007; Bassi et al., 2008) têm discutido a necessidade de excitação individual de cada elemento, envolvendo uma relação entre a complexidade dos circuitos eletrônicos e o desempenho adequado do transmissor para otimizar a qualidade das imagens médicas. Embora os equipamentos comerciais de US sejam amplamente empregados para auxílio ao diagnóstico médico, o acesso à configuração e controle dos circuitos de transmissão bem como a aquisição dos sinais de ecos ultrassônicos refletidos são restritos, impossibilitando a pesquisa de novas técnicas de excitação e modalidades do US (Bassi et al., 2008). Projetados para uso clínico, possuem arquitetura típica "fechada", não atendendo às exigências de flexibilidade para programação e atualização, necessários para a implementação de novas abordagens.

Neste artigo objetiva-se apresentar a concepção e o desenvolvimento de uma arquitetura flexível de hardware baseada em FPGA, totalmente configurável e modular, para controle individual de 8 canais de transmissão e geração de forma de onda arbitrária, para aplicações de pesquisa do US. O sistema beamformer digital de transmissão permite controle independente da amplitude de apodização, ângulo de fase e atraso temporal de disparo para cada canal. Em conjunto com os circuitos de excitação, foram inseridos os circuitos de condicionamento e proteção dos canais de recepção, possibilitando o processamento dos ecos de RF (Radio Frequency) em trabalhos futuros. Serão apresentadas nas próximas seções a descrição das principais técnicas de excitação para US, e a análise detalhada do sistema desenvolvido, com o objetivo de ilustrar as características do mesmo.

#### **CIRCUITOS GERADORES DE PULSOS** 2 DE EXCITAÇÃO

Nos sistemas de US, o módulo eletrônico lógico para formação do feixe é responsável por enviar pulsos elétricos de alta tensão ao conjunto de elementos piezoelétricos e estes os convertem em ondas de pressão utrassônicas. De forma geral, quatro topologias são empregadas para excitação dos transdutores: transmissão com pulsos unipolares, pulsos bipolares, excitação multinível e forma de onda arbitrária de US.

#### 2.1 Circuito de transmissão com pulsos unipolares

Devido ao baixo custo e facilidade na implementação, circuitos geradores de pulso unipolares de alta tensão (HV high voltage) ainda são usados com frequência na unidade de transmissão (Brown & Lockwood, 2002). Embora não permitam otimização na qualidade da imagem, novos projetos e implementações têm demonstrado que a técnica pode ser utilizada para novas aplicações, como por exemplo, excitação de arranjos lineares de elementos de alta frequência (HF – high frequency) ou HF phased array (> 50 MHz), com circuitos mais simples e compactos (Hu et al., 2008).

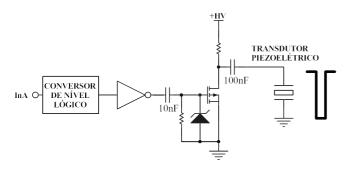

A Figura 1 apresenta o exemplo de um circuito gerador de pulso unipolar. Esta unidade é composta pelo buffer conversor de nível lógico, driver de corrente, e circuito de potência. Na interface lógica de entrada InA, é aplicado o pulso lógico de disparo, com largura na ordem de dezenas de nanosegundos, ao circuito formado pelo buffer de tensão e driver de corrente. Em seguida, o sinal condicionado dispara o transistor de potência MOSFET canal N, com dreno conectado em uma fonte de alta tensão. Quando é aplicado o pulso de disparo, o MOSFET conduz, e toda a tensão armazenada no capacitor de 100 nF é aplicada ao transdutor, porém com polaridade invertida (Assef et al., 2009).

Figura 1: Circuito esquemático simplificado de um gerador de pulso de excitação unipolar.

#### 2.2 Circuito de transmissão com pulsos bipolares

Circuitos geradores de pulsos bipolares de onda quadrada são comumente utilizados para acionar os elementos transdutores nos equipamentos comerciais de US atuais (Brunner, 2002) e empregam técnicas bem estabelecidas para geração de imagem (Brown & Lockwood, 2002). Devido à alta tensão aplicada, geralmente entre  $\pm 100$  V, esses circuitos permitem obter uma maior sensibilidade com melhoria na relação sinal-ruído (SNR – Signal-to-Noise Ratio), bem como uma boa penetração do campo acústico. Para aplicações Doppler,

permitem uma maior eficiência na geração de imagens (Xu et al., 2007).

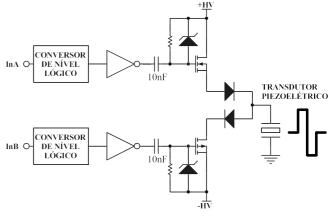

Um esquema básico para geração de pulsos bipolares é apresentado na Figura 2. O circuito é bastante similar ao unipolar, porém são utilizados dois MOSFETS complementares, canais N e P, na configuração push-pull com capacidade de prover correntes de pico acima de 2 A, para excitação com onda quadrada de alta tensão. Para o exemplo, pulsos lógicos de disparo são aplicados às entradas InA e InB alternadamente, excitando o transdutor com as tensões positiva e negativa das fontes de alta tensão, controlados pelo beamformer de transmissão.

Figura 2: Circuito esquemático simplificado de um gerador de pulso de excitação bipolar.

## Circuito de transmissão com pulsos bipolares multinível

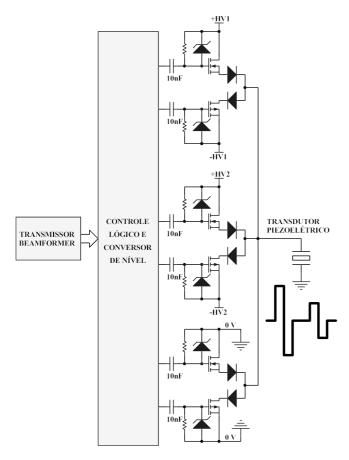

A implementação de circuitos de transmissão mais complexos, com múltiplas fontes de alimentação, permite a geração de pulsos bipolares multinível de alta tensão, e formas de onda com melhores características (Ricci et al., 2007). Nessa topologia, são utilizados circuitos integrados (CIs) drivers de US multicanais com elevada integração, que operam em alta velocidade, e possuem entradas lógicas para controle individual dos canais de excitação. As interfaces de saída consistem de *drivers* de corrente para excitar o respectivo par complementar de MOSFETs de alta tensão. A Figura 3 apresenta o circuito esquemático simplificado de um gerador de pulsos bipolares com 5 níveis: +HV1, -HV1, +HV2, -HV2 e 0 V.

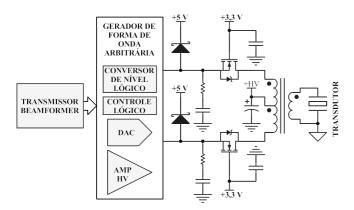

### Circuito gerador de forma de onda arbitrária de US

O estado da arte na forma de transmissão é a geração de formas de onda complexas utilizando geradores de onda arbi-

Figura 3: Circuito de transmissão simplificado para excitação multinível (5 níveis).

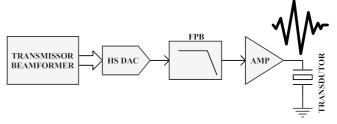

trária de US (Maxim Integrated Products, 2011). Nestes casos, o transmissor beamformer gera o controle digital, tipicamente entre 8 e 12 bits, com elevada taxa de comunicação (> 20 MHz) para otimizar a qualidade da imagem (Olympus NDT, 2007). Conversores digital para analógico de alta velocidade (HS DAC – *High-Speed Digital-to-Analog Converter*) são usados para converter a forma de onda digital para um sinal analógico, que é aplicado ao filtro passa-baixas (FPB) para eliminar a alta frequência de chaveamento. O sinal filtrado é aplicado ao amplificador com controle linear de alta tensão classe AB para excitação dos elementos transdutores (Jensen et al., 2005). Esta técnica de transmissão é geralmente reservada para os sistemas mais caros e menos portáteis, pois necessita de drivers mais complexos e com maior consumo de potência, consequentemente, aumentando o tamanho do equipamento (Maxim Integrated Products, 2011). A Figura 4 apresenta o diagrama em blocos do circuito de excitação para geração de forma de onda arbitrária de US.

Figura 4: Diagrama em blocos do circuito de excitação para geração de forma de onda arbitrária de US.

# ESPECIFICAÇÕES DE REQUISITOS

O circuito beamformer digital de transmissão tem a função de gerar os sinais digitais de transmissão necessários para controle individual de fase, amplitude e atraso de cada elemento do transdutor, possibilitando produzir um sinal de transmissão focalizado. A partir desta definição, foi elaborada a especificação de requisitos para a concepção e desenvolvimento do sistema. Esta especificação é apresentada na Tabela 1 com as definições dos parâmetros necessários para configuração e geração das formas de onda arbitrárias de US. Além disso, são definidas as interfaces físicas para configuração, controle e sinalização do sistema proposto.

Tabela 1: Especificações de requisitos do sistema.

| Especificação                                                       |

|---------------------------------------------------------------------|

| Controle digital através de FPGA                                    |

| 8 canais de transmissão independentes                               |

| Indicação visual do estado do equipamento e confi-                  |

| gurações através de <i>display</i> de cristal líquido $16 \times 2$ |

| e LEDs                                                              |

| Configuração de parâmetros e funções do sistema                     |

| através de 4 chaves tipo push-button                                |

| Comunicação USB                                                     |

| Modo de operação pulso-eco                                          |

| Taxa de repetição dos pulsos de excitação entre                     |

| 62,5 Hz e 8 kHz, ou pulso único                                     |

| Frequência central entre 500 kHz e 20 MHz                           |

| Tensão de excitação entre -100 V e +100 V                           |

| Ângulo de fase entre $0^{\circ}$ e $360^{\circ}$                    |

| Amplitude de apodização com resolução de 8 bits                     |

| através de DAC                                                      |

| Atraso de disparo com resolução < 10 ns                             |

| Circuitos de proteção dos canais de recepção                        |

| Conectores SMA para conexão com placas de ava-                      |

| liação com circuito AFE                                             |

| Forma de onda com perfil Gaussiano                                  |

|                                                                     |

## SISTEMA BEAMFORMER DIGITAL DE TRANSMISSÃO PROPOSTO

Com base nas especificações apresentadas na seção 3, foi realizada uma pesquisa sobre os módulos de hardware, software e demais componentes necessários para o projeto, resultando nos módulos descritos nesta seção.

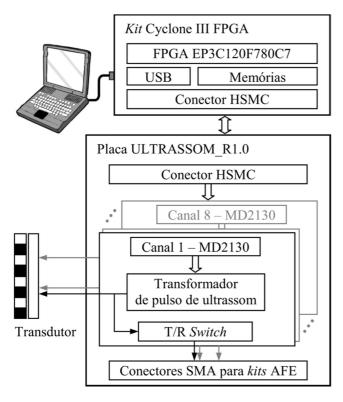

Na Figura 5 é apresentado o diagrama em blocos completo da arquitetura de transmissão proposta, composto basicamente por duas placas: Cyclone III FPGA Development Board e placa ULTRASOM\_R1.0.

Figura 5: Diagrama em blocos do sistema beamformer de transmissão para aplicações de US proposto.

O kit de desenvolvimento Cyclone III FPGA foi adotado como placa-mãe para a implementação do protótipo. A placa utiliza o FPGA EP3C120F780 da família Cyclone III, com 119088 elementos lógicos, 3888 kbits de memória, e 531 pinos livres de I/O (Input-Output) (Altera, 2010), atendendo todos os pré-requisitos de hardware, como processamento paralelo e lógica reconfigurável, com elevado desempenho para controle e gerenciamento das interfaces do sistema. O kit também possui diversas memórias externas, interfaces de comunicação USB e Ethernet, quatro chaves, oito LEDs e um display LCD 16 x 2. Além disso, como item fundamental para o protótipo, o kit da Altera Corporation dispõe de um conector de expansão HSMC (High-Speed Mezzanine Card), com 172 pinos, sendo 52 pinos para alimentação e o restante

para sinais de I/O com nível de 2,5 V. Destes, 80 pinos são utilizados (10 pinos por canal), possibilitando o controle individual dos 8 canais de transmissão pelo dispositivo FPGA.

A segunda é a placa-filha ULTRASOM\_R1.0, que é interligada à placa-mãe Cyclone III através do conector de expansão. A placa é composta por 8 conjuntos de CIs MD2130, MOSFETs de alta tensão, transformadores de US, conectores para transdutores monoelemento e multielementos, circuitos de proteção de recepção (T/R switches) e conectores do tipo SMA. A inclusão destes conectores possibilita o interfaceamento do sistema proposto com placas de avaliação baseadas em dispositivos AFE (Analog Front-End), para leitura dos ecos de RF e processamento do beamformer de recepção, como por exemplo, as placas AFE5805EVM (Texas Instruments, 2008) e HSC-ADC-EVALC (Analog Devices, 2007) para sistemas de US.

#### 4.1 Circuito integrado MD2130

Para atender às especificações definidas na seção 4, foi escolhido o dispositivo MD2130 (Supertex Inc.), como driver de alta velocidade para geração de forma de onda arbitrária de US. O CI possui quatro fontes de corrente PWM (Pulse Width Modulation), controladas individualmente pelo FPGA, e um DAC de corrente de 8 bits para controle da amplitude de apodização da forma de onda. Os quatro sinais PWM de alta velocidade que controlam o formato da onda de saída são divididos em: IA, IB - sinais em fase -, e QA e QB - sinais em quadratura. Os sinais IA e QA, controlam a amplitude dos semiciclos positivos, enquanto IB e QB, a amplitude dos semiciclos negativos. Além disso, possui uma interface serial SPI (Serial Peripheral Interface) que opera em 20 MHz e permite atualização rápida do comutador da matriz I/Q do vetor ângulo do *beamforming*, com resolução angular de 7,5° por passo (total de 48 passos – 6 bits), e da amplitude de apodização (total de 255 passos - 8 bits) (Supertex, 2009). No estágio de saída de cada MD2130, são conectados dois MOS-FETs DN2625 de alta tensão que operam como fonte de corrente na configuração *push-pull*, com capacidade de até 3 A. Os drenos dos MOSFETs são conectados na derivação central dos transformadores de US, enquanto os enrolamentos secundários são conectados aos elementos transdutores ou cargas equivalentes para testes, formadas por um capacitor de 220 pF em paralelo com um resistor de 1 k $\Omega$ . A Figura 6 mostra o circuito esquemático simplificado para conexão com o CI MD2130.

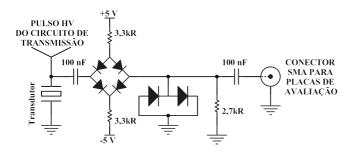

#### Circuitos de proteção – T/R Switches 4.2

Na operação em modo pulso-eco o transdutor, que é excitado com os pulsos elétricos de alta amplitude, também capta os sinais de US na recepção. Com isso, é necessário um cir-

Figura 6: Circuito esquemático simplificado para conexão com o CI MD2130.

Figura 7: Circuito de proteção para a unidade de recepção contra sobrecarga.

cuito de proteção T/R switch para evitar que transitórios de alta tensão danifiquem o circuito amplificador de baixo ruído (LNA - Low Noise Amplifier) da unidade de recepção, que poderá ser conectado ao sistema proposto. A Figura 7 ilustra o circuito de proteção contra sobretensão implementado, formado por quatro diodos de alta tensão na configuração ponte. Embora os diodos idealmente bloqueiem os pulsos de transmissão da entrada de recepção, é comum que transientes rápidos até alguns Volts passem pelo T/R switch, e potencialmente sobrecarreguem o receptor. Portanto, um par adicional de diodos back-to-back de alta velocidade foi inserido entre o T/R switch e conector SMA de saída para o pré-amplificador do circuito de recepção. A fim de manter a sobretensão em níveis de  $\pm 0.5$  V, ou menos, diodos BAV99 de alta velocidade foram usados para melhorar o desempenho de recuperação de sobrecarga. A Figura 7 também mostra que a saída do circuito de proteção possui acoplamento capacitivo com o próximo estágio de recepção, garantindo que a tensão de entrada de polarização da unidade seja desacoplada de qualquer outra tensão do circuito anterior.

## **DETERMINAÇÃO DOS SINAIS EM FASE E QUADRATURA**

Esta seção apresenta o método matemático utilizado para determinação dos quatro sinais PWM de alta frequência, em fase e quadratura, que devem ser gerados pelo FPGA para formação do sinal arbitrário de US. Para a análise, os valores iniciais dos parâmetros são apresentados na Tabela 2.

Tabela 2: Considerações para geração dos sinais PWM em fase I e quadratura Q.

| Parâmetro                          | Atribuição         |

|------------------------------------|--------------------|

| Forma de onda dos sinais $I$ e $Q$ | Envelope Gaussiano |

| Frequência central                 | 20 MHz             |

| Frequência de amostragem $(f_s)$   | 320 MHz            |

| Número de amostras por ciclo       | 320/20 = 16        |

| Número de amostras por semiciclo   | 8 (0 - 7)          |

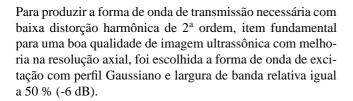

| Largura de banda relativa          | 50 % (-6 dB)       |

| Número total de amostras           | 128                |

Sejam os sinais em fase i(t) e quadratura q(t) contínuos no tempo, e i(n) e q(n) seus correspondentes sinais discretos no tempo amostrados na frequência  $f_s$  (equações (1) e (2)):

$$i(n) = i(t) \big|_{t=n/f_s} \tag{1}$$

$$q(n) = q(t) \mid_{t=n/fs} \tag{2}$$

onde t denota tempo e a letra n o índice de tempo discreto.

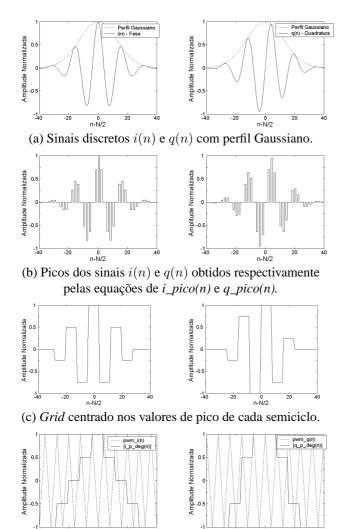

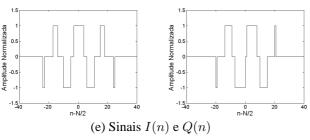

As equações dos sinais em fase i(n) e quadratura q(n) (Figura 8(a)) com o envelope do perfil Gaussiano são apresentadas no domínio discreto (equações (3) e (4)) (Assef et al., 2010):

$$i(n) = \exp\left[-\left(\frac{n - \frac{N}{2}}{B}\right)^2\right] \cdot \cos\left(2\pi \frac{n}{T}\right), 1 \le n \le N$$

(3)

$$q(n) = \exp\left[-\left(\frac{n - \frac{N}{2}}{B}\right)^{2}\right] \cdot sen\left(2\pi \frac{n}{T}\right), 1 \le n \le N$$

(4)

onde N é o número total de amostras, T é o período para um ciclo e B é o fator de largura de banda do envelope Gaussi-

Figura 8: Seguência de formas de onda para geração dos sinais em fase I(n) e em quadratura Q(n).

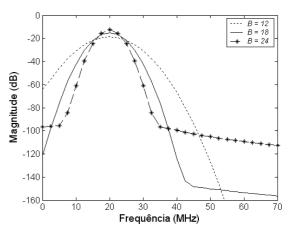

A influência do fator B nas equações (3) e (4) pode ser verificada na Figura 9, para determinação da largura de banda relativa. A Figura 9 mostra o espectro de frequência para três valores diferentes de B, com frequência central de 20 MHz. Quanto menor o valor de B, maior a largura de banda rela-

Figura 9: Influência do fator B para determinação da largura relativa de banda dos sinais i(t) e q(t).

tiva do sinal. Neste trabalho, foi adotado o valor de B igual a 18, resultando em uma largura de banda relativa de 50 %, com frequências de corte inferior e superior em -6 dB, iguais a 15 MHz e 25 MHz, respectivamente.

Sabendo que valores máximos e mínimos das funções seno e cosseno estão localizados em kT/2 e kT/2 - T/4 ( $k \ge 0$ ), respectivamente, são calculadas as posições dos picos positivo  $(x_{pico\_i})$  e negativo  $(x_{pico\_q})$  de cada semiciclo (equações (5) e (6)):

$$x_{pico_{\underline{i}}}(n) = \operatorname{mod}\left(\frac{n}{T/8}\right), 1 \le n \le N$$

(5)

$$x_{pico_{q}}(n) = \operatorname{mod}\left(\frac{n - T/4}{T/8}\right), 1 \le n \le N$$

(6)

onde a função *mod* representa o resto da divisão indicada.

Os valores de pico são encontrados através das equações (7) e (8) (Figura 8(b)):

$$i\_pico(n) = \begin{cases} i(n) & \text{se } x_{pico\_i}(n) = 0\\ 0 & \text{caso contrário} \end{cases}$$

(7)

$$q\_pico(n) = \begin{cases} q(n) & \text{se } x_{pico\_q}(n) = 0\\ 0 & \text{caso contrário} \end{cases}$$

(8)

Posteriormente, o valor máximo de cada semiciclo positivo é adotado para o grid de todas as amostras do mesmo semiciclo, ocorrendo da mesma forma para o semiciclo negativo, resultando nos sinais  $i_p_{deg}(n)$  e  $q_p_{deg}(n)$  (Figura 8(c)) como degraus de referência para cada semiciclo. Na sequência os valores absolutos dos degraus  $i_p_{deg}(n)$  e  $q_p_{deg}(n)$ , são comparados com os sinais PWM -  $pwm_i(n)$ e  $pwm_{q}(n)$  - de cada semiciclo (Figura 8(d)). Como resultado, são gerados os sinais de referência  $i \ ref(n)$  e  $q \ ref(n)$ (equações (9) e (10)).

$$i_ref(n) = pwm_i(n) - |i_p_{deg}(n)|, 1 \le n \le N$$

(9)

$$q_ref(n) = pwm_q(n) - |q_p_{\deg}(n)|, 1 \le n \le N$$

(10)

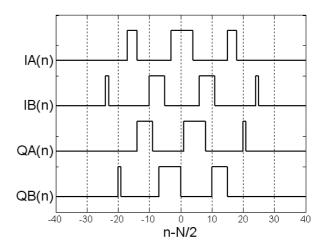

A partir dos sinais de referência são obtidos os sinais em fase I(n) e quadratura Q(n) (equações (11) e (12) - Figura 8(e)). Cada sinal é decomposto em dois outros sinais, sendo um para o semiciclo positivo e outro para o negativo (equações (13), (14), (15) e (16)), resultando nos quatro sinais lógicos PWM, apresentados na Figura 10, para geração da forma de onda.

$$I(n) = \begin{cases} \frac{i_- p_- \deg(n)}{|i_- p_- \deg(n)|} & \text{se } i_- ref(n) > 0\\ 0 & \text{caso contrário} \end{cases}$$

(11)

$$Q(n) = \begin{cases} \frac{q_{-p_{-}}\deg(n)}{|q_{-p_{-}}\deg(n)|} & \text{se } q_{-}ref(n) > 0\\ 0 & \text{caso contrário} \end{cases}$$

(12)

$$IA(n) = \begin{cases} 1 & \text{se } I(n) > 0\\ 0 & \text{caso contrário} \end{cases}$$

(13)

$$IB(n) = \begin{cases} 1 & \text{se } I(n) < 0 \\ 0 & \text{caso contrário} \end{cases}$$

(14)

$$QA(n) = \begin{cases} 1 & \text{se } Q(n) > 0\\ 0 & \text{caso contrário} \end{cases}$$

(15)

$$QB(n) = \begin{cases} 1 & \text{se } Q(n) < 0 \\ 0 & \text{caso contrário} \end{cases}$$

(16)

#### **RESULTADOS EXPERIMENTAIS** 6

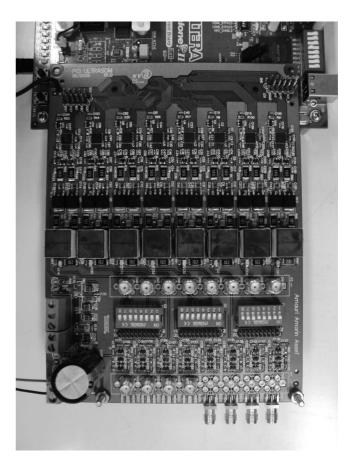

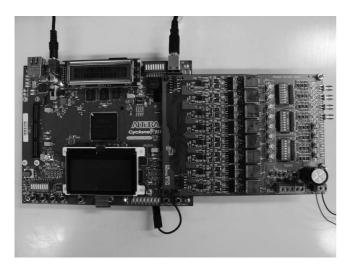

O layout da placa protótipo ULTRASOM\_R1.0 desenvolvida é apresentado na Figura 11. A placa foi confeccionada com tecnologia de circuito impresso dupla face e possui dimensão de 171 x 127 mm. A Figura 12 mostra o protótipo completo do sistema proposto, formado pelas placas Cyclone III FPGA Development Board e ULTRASOM R0.1.

Figura 10: Sinais lógicos PWM de excitação para cada canal - IA(n), IB(n), QA(n) e QB(n).

Figura 11: Layout da placa ULTRASOM\_R1.0 com dimensão de 171 x 127 mm.

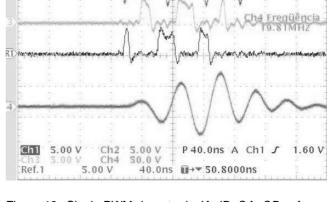

A Figura 13 apresenta os sinais lógicos PWM de entrada IA (CH1), IB (CH2), QA (CH3) e QB (Ref1) gerados pelo FPGA, e a forma de onda na carga equivalente (CH4), com

Figura 12: Protótipo do sistema de transmissão proposto formado pelas placas ULTRASOM\_R1.0 e Cyclone III FPGA Development Board.

Figura 13: Sinais PWM de entrada IA, IB, QA, QB, e forma de onda de gerada na carga equivalente.

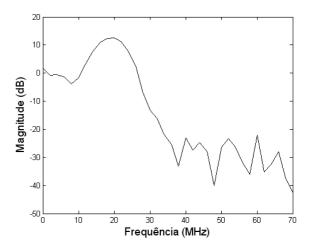

frequência de 20 MHz e amplitude de 89 Vpp. O espectro de frequência do sinal de excitação é apresentado na Figura 14. O canal de transmissão utilizado foi configurado com ângulo de fase e atraso de disparo nulos, e DAC com fator multiplicador igual a 255 (100 %) para a amplitude de apodização.

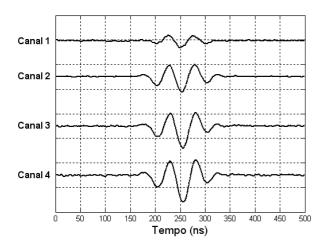

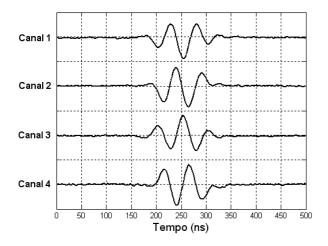

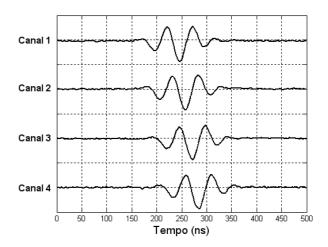

Para ilustrar o funcionamento do sistema de transmissão proposto, são mostradas nas Figuras 15, 16 e 17 as comparações entre os ajustes individuais de quatro canais de excitação na carga equivalente, com tensão de alimentação de +70 V e frequência de 20 MHz. A Figura 15 apresenta as formas de ondas geradas para o DAC configurado com 64 (25,1%), 128 (50,2 %), 192 (75,3 %) e 255 (100 %). Na Figura 16 são mostradas as formas de ondas geradas para o ângulo de fase igual a 0°, 90°, 180° e 270°. A Figura 17 ilustra o atraso temporal na transmissão para os valores nulo, 12,5 ns, 25,0 ns, e 37,5 ns, respectivamente, com resolução de 3,13 ns (1/320 MHz). Nas Figuras 16 e 17 o valor do DAC foi ajustado para 240 (94,1 %) para melhor representação.

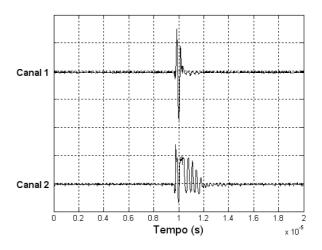

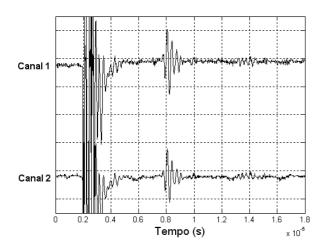

Para avaliação do circuito T/R switch, foi utilizado um transdutor multielemento convexo, com frequência central de 3,5 MHz, imerso em um tanque com 10 litros de água. Um cilindro de alumínio com espessura de 19 mm foi utilizado para o teste no modo pulso-eco, conforme descrito por Assef et al. (2009). A Figura 18 mostra os sinais de excitação na entrada (Canal 1) e saída (Canal 2) do circuito de proteção, com escala vertical de 20 V/divisão e 500 mV/divisão, respectivamente. Observa-se que a amplitude de 68 Vpp do sinal de excitação foi limitada em 1,1 Vpp pelo circuito de proteção. A atuação do circuito também é ilustrada na Figura 19, sendo que os Canais 1 e 2 mostram os ecos de US, na entrada e saída do módulo de proteção, com escala

Figura 14: Espectro de frequência da forma de onda gerada na carga equivalente.

vertical de 100 mV/divisão. Neste teste, pode-se notar que o formato da onda de ecos do Canal 1, com amplitude de 255 mVpp, foi preservado, e que o sinal do Canal 2, com amplitude 195 mVpp, apresentou atenuação de 2,3 dB.

# **CONCLUSÕES**

Neste trabalho, foi apresentado o desenvolvimento de uma arquitetura totalmente programável, "aberta" e flexível, baseada em FPGA, com 8 canais para geração do beamformer de transmissão (Tx beamformer) com formas de ondas arbitrárias para auxílio às atividades de pesquisa do US.

Figura 15: Comparação das formas de ondas de saída com DAC ajustado para 64 (Canal 1), 128 (Canal 2), 192 (Canal 3) e 255 (Canal 4) - escala vertical de 50 V/divisão.

Figura 16: Comparação das formas de ondas de saída com ângulo de fase ajustado para 0° (Canal 1), 90° (Canal 2),  $180^{\circ}$  (Canal 3) e  $270^{\circ}$  (Canal 4) - escala vertical de 50 V/divisão.

A metodologia empregada para o cálculo da largura dos sinais lógicos PWM necessários para a geração de formas de ondas com perfil Gaussiano e frequência central de 20 MHz, realizada através de simulações com o software Matlab (The MathWorks Inc.), foi comprovada nos resultados práticos

Figura 17: Comparação entre as formas de ondas de saída com atraso de transmissão ajustado para 0,0 ns (Canal 1), 12,5 ns (Canal 2), 25,0 ns (Canal 3) e 37,5 ns (Canal 4) escala vertical de 50 V/divisão.

Figura 18: Comparação entre os sinais antes (Canal 1) e após o circuito de proteção (Canal 2) - escala vertical de 20 V/divisão (Canal 1) e 500 mV/divisão (Canal 2).

com cargas equivalentes, atendendo às expectativas do projeto.

Considerando a largura dos sinais em fase e quadratura obtidos, limitada entre os valores 0 (0 %) e 7 (100 %) para a frequência de amostragem de 320 MHz, conforme especificado na Tabela 2, foi desenvolvida a programação do dispositivo FPGA de 119088 elementos lógicos em linguagem VHDL. A arquitetura utilizou em torno de 5 % dos recursos disponíveis do FPGA, para controle e configuração do sistema, e geração dos 32 canais PWM (8 canais para cada CI MD2130) de forma totalmente paralela. Com isso, trabalhos

Figura 19: Ecos ultrassônicos recebidos antes (Canal 1) e após (Canal 2) o circuito de proteção - escala vertical de 100 mV/divisão.

futuros poderão explorar outras funcionalidades do FPGA, como por exemplo, inclusão de componentes SOPC (*System on a Programmable Chip*) como microprocessadores de 32 *bits* com interfaces de comunicação USB e *Ethernet*, com programação em linguagem *Assembly* ou C, possibilitando alteração de configurações, parâmetros, formas de onda de excitação, protocolos de teste e demais funcionalidades, utilizando um microcomputador.

Os circuitos de proteção T/R *switches* foram validados e apresentaram baixa atenuação na faixa do sinal de interesse, possibilitando a leitura dos ecos de RF e interface de forma segura com sistemas AFE, para futuras pesquisas envolvendo o processamento do *beamformer* de recepção.

Os resultados com diferentes configurações para comparação entre a amplitude de apodização, ângulo de fase e atraso temporal de transmissão para quatro canais, são apresentados e corroboram que a utilização do dispositivo FPGA, juntamente com os CIs MD2130, permite total flexibilidade para programação e atualização, e validam o sistema proposto como uma plataforma reconfigurável adequada e viável para pesquisas experimentais do US.

#### **AGRADECIMENTOS**

Os autores agradecem ao Departamento de Engenharia Biomédica (DEB) da Faculdade de Engenharia Elétrica e de Computação (FEEC) da Universidade Estadual de Campinas (UNICAMP), e ao CNPq pelo apoio financeiro para o desenvolvimento da pesquisa.

## REFERÊNCIA BIBLIOGRÁFICA

- Altera Corporation (2010). Cyclone III Device Handbook I-II. Altera Handbook, San Jose, CA, USA.

- Analog Devices Inc. (2007). High Speed Converter Evaluation Platform - HSC-ADC-EVALC. Data sheet, Norwood, MA, USA.

- Assef, A. A., Maia, J. M., Armstrong, R. B., Ashihara, H. M., Costa, E. T., Button, V. L. da S. N. (2010). Sistema digital gerador de forma de onda arbitrária para aplicações de ultrassom. *XXII Congresso Brasileiro de Engenharia Biomédica (CBEB) 2010*, Tiradentes, MG, Brasil, p. 391-394.

- Assef, A. A., Maia, J. M., Gewehr, P. M., Gamba H. R., Costa, E. T., Button, V. L. S. N. (2009). Sistema para geração, aquisição e processamento de sinais de ultrasom. Sba Controle & Automação, vol. 20, n° 2, p. 145-155.

- Basoglu, C., Managuli, R. York, G., Kim, Y. (1998). Computing requirements of modern medical diagnostic ultrasound machines. *Parallel Computing*, v. 24, p. 1407-1431.

- Bassi, L., Boni, E., Cellai A., Dallai, A., Guidi, F., Ricci, S., Tortoli, P. (2008). A Novel Digital Ultrasound System for Experimental Research Activities. 11th Euromicro Conference on Digital System Design Architectures, Methods and Tools, p. 413-417.

- Brown, J. A., Lockwood, G. R. (2002). A low-cost, highperformance pulse generator for ultrasound imaging. *IEEE Transactions on Ultrasonics, Ferroelectrics, and Frequency Control*, vol. 49, n° 6, p. 848-851.

- Brunner, E. (2002). Ultrasound system considerations and their impact on front-end components. Application Note, Analog Devices, Norwood, MA, USA.

- Huang, S. W., Li, P. C. (2006). Arbitrary Waveform Coded Excitation Using Bipolar Square Wave Pulsers in Medical Ultrasound. *IEEE Transactions on Ultrasonics*, *Ferroelectrics, and Frequency Control*, vol. 53, n° 1, p. 106-116.

- Hu, C. H., Zhou, Q., Shung, K. K. (2008). Design and Implementation of High Frequency Ultrasound Pulsed-Wave Doppler Using FPGA. *IEEE Transactions on Ultrasonics, Ferroelectrics, and Frequency Control*, vol. 55, n° 9, p. 2109-2111.

- Jensen, J. A., Holm, O., Jensen, L. J., Bendsen H., Nikolov S. I., Tomov, B. G., Munk, P., Hansen, M., Kent, Salomonsen, J. H., Gormsen, K., Pedersen, H. M., Gammelmark, K. L. (2005). Ultrasound Research Scanner for

- Real-time Synthetic Aperture Data Acquisition. *IEEE Transactions on Ultrasonics, Ferroelectrics, and Frequency Control*, vol. 52, n° 5, p. 881-889.

- Kim, Y., Kim, J. H., Basoglu, C., Winter, T. (1997). Programmable ultrasound imaging using multimedia technologies: A next-generation ultrasound machine. *IEEE Transactions on Information Technology in Biomedicine*, v. 1, p. 19-29.

- Mahdy, E. R., Khalil, R. M., Sherif S., Kadah, Y. M. K. (2006). FPGA Based Backend System for Medical B-Mode Ultrasound Imaging. Proc. Cairo International Biomedical Engineering Conference.

- Maxim Integrated Products (2011). Medical imaging: Ultrasound imaging systems. Application Note, Sunnyvale, CA, USA.

- Misaridis, T., Jensen, J. A. (2005). Use of modulated excitation signals in ultrasound. Part I: Basic concepts and expected benefits. *IEEE Transactions on Ultrasonics, Ferroelectrics, and Frequency Control*, v. 50, p. 192-207.

- Olympus NDT (2007). Introduction to Phased Array Ultrasonic Technology Applications: R/D Tech Guideline. Olympus NDT, MA, USA.

- Park, J. H., Yoon, C., Chang, J. H., Yoo, Y., Song, T. K. (2010). A Real-time Synthetic Aperture Beamformer for Medical Ultrasound Imaging. *IEEE Ultrasonics Symposium (IUS)*, p. 1992 1995.

- Ricci, S., Bassi, L., Boni, E., Dallai, A., Tortoli, P. (2007). Multichannel FPGA-based arbitrary waveform generator for medical ultrasound. *IET Electronics Letters*, vol. 43, p. 1335-1336.

- Schneider, F.K., Agarwal, A., Yang Mo Yoo, Fukuoka, T., Kim, Y. (2010). A Fully Programmable Computing Architecture for Medical Ultrasound Machines. *IEEE Transactions on Information Technology in Biomedicine*, vol. 14, p. 538-540.

- Silkdar, S., Managuli, R., Gong, L. (2003). A single mediaprocessor-based programmable ultrasound system. *IEEE Transactions on Information Technology in Biomedicine*, v. 7, p. 64-70.

- Supertex Inc. (2009). MD2130 High Speed Ultrasound Beamforming Source Driver. Data sheet, Sunnyvale, CA. USA.

- Texas Instruments Inc. (2008). AFE5805 Fully-Integrated, 8-channel analog front-end for ultrasound. Data sheet, Dallas, Texas, USA.

- Tomov, B. G., Jensen, J. A. (2005). Compact FPGA-Based Beamformer Using Oversampled 1-bit A/D Converters. *IEEE Transactions on Ultrasonics, Ferroelectrics, and Frequency Control*, vol. 52, p. 870-880.

- Xu, X., Yen, J. T., Shung, K. K. (2007). A Low-Cost Bipolar Pulse Generator for High-Frequency Ultrasound Applications. *IEEE Transactions on Ultrasonics, Fer*roelectrics, and Frequency Control, vol. 54, n° 2, p. 443-447.

- Zhou, S., Hossack, J. A. (2003). Dynamic-transmit focusing using time dependent focal zone and center frequency. *IEEE Transactions on Ultrasonics, Ferroelectrics, and Frequency Control*, v. 50, p. 142-152.